IRIET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

# **Digital clock using FPGA**

D.N.J Sandhya<sup>1</sup>, M.R.S.N visranthamm<sup>2</sup>, Ch.Deepthi<sup>3</sup>, G.Poojasri<sup>4</sup>, K.Chandra Sekhar<sup>5</sup>

<sup>1</sup>Student & AMRITA SAI INSTITUTE OF SCIENCE AND TECHNOLOGY <sup>2</sup>Assistant Professor & AMRITA SAI INSTITUTE OF SCIENCE AND TECHNOLOGY <sup>3</sup>Student & AMRITA SAI INSTITUTE OF SCIENCE AND TECHNOLOGY <sup>4</sup>Student & AMRITA SAI INSTITUTE OF SCIENCE AND TECHNOLOGY <sup>5</sup>Student & AMRITA SAI INSTITUTE OF SCIENCE AND TECHNOLOGY

#### **Abstract** -

This research presents the design and implementation of a digital clock integrated with a stopwatch feature using Field Programmable Gate Array (FPGA) technology. The project utilizes Verilog Hardware Description Language (HDL) to create a multifunctional timekeeping system capable of operating in two modes: digital clock and stopwatch. The clock mode displays time in minutes and seconds (MM:SS), while the stopwatch mode allows the user to start, stop, and reset elapsed time. Mode selection and control are handled through input signals, offering a flexible and user-interactive experience.

The architecture includes key modules such as Digi for clock functionality, stop for stopwatch control, and Display for 7-segment display decoding. Timing is accurately managed using two internal clock dividers: one for generating a 1Hz signal for time progression and another for refreshing the 4-digit 7-segment display. Multiplexing logic is employed to drive the display efficiently, providing clear visual feedback of the current time or stopwatch values.

The FPGA-based approach ensures high-speed operation, precise timing, and reconfigurability without requiring external microcontrollers. The design is synthesized and tested on an FPGA development board, confirming correct functionality under various input conditions. This project not only demonstrates the capabilities of FPGAs in digital system design but also provides an educational platform for understanding realtime hardware control and display interfacing. The implementation highlights the potential of FPGAs in embedded systems where reliability, performance, and real-time response are critical.

**Keywords:** FPGA (Field Programmable Gate Array), Digital Clock ,Stopwatch ,Verilog HDL ,7-Segment Display ,Timekeeping ,Clock Divider ,Multiplexing ,Embedded Systems, Real-Time Systems, Digital Electronics

### 1.INTRODUCTION

In the current landscape of digital electronics and embedded systems, the importance of timekeeping

mechanisms has become more significant than ever. Time has always been a vital parameter in the operation and regulation of processes, not just in human life but also in machine operations. From microcontrollers regulating home appliances to high-performance processors synchronizing tasks across network systems, time forms the foundation of reliable execution. Among various methods of timekeeping, digital clocks remain one of the most widely utilized and illustrative systems, offering both functionality and conceptual clarity in understanding realtime digital systems. One of the most instructive and functionally rich platforms for implementing such systems is the Field Programmable Gate Array (FPGA), which offers designers immense flexibility and control over hardware behavior. This research project focuses on the design and implementation of a digital clock system using FPGA technology, incorporating additional features such as a stopwatch and dynamic mode switching, all controlled and developed through the Verilog Hardware Description Language (HDL).

Historically, digital clocks have evolved from simple seven-segment LED-based designs to integrated LCD and OLED displays with microcontroller-driven intelligence. These systems, while effective in delivering user-friendly interfaces and timekeeping functionalities, often face constraints in speed, flexibility, and performance when scaled or modified. This is where FPGA-based systems shine. Unlike microcontrollers or ASICs (Application-Specific Integrated Circuits), FPGAs allow developers to redefine hardware behavior dynamically without redesigning the physical circuitry. This makes FPGAs highly advantageous for time-critical require applications and system designs that customization, real-time responsiveness, and parallelism.

FPGA devices are semiconductor components that consist of a matrix of configurable logic blocks (CLBs) interconnected via programmable routing. By using a hardware description language such as Verilog, designers can define the logical behavior of a circuit, which is then mapped onto the FPGA's resources. This methodology the latency introduced by eliminates interpretation in traditional microcontroller systems and brings about deterministic, hardware-level control. For a

IRIET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net

timekeeping device such as a digital clock, this results in extremely precise timing accuracy, efficient control mechanisms, and the ability to incorporate complex features like stopwatches, alarms, and event timers—all on a single programmable platform.

The motivation behind this project stems not only from the desire to create a fully functional digital clock system but also from the educational and developmental value it provides. This project embodies the core principles of digital electronics—timing, counting, state machines, multiplexing, display interfacing, and user interaction—all wrapped within a practical and familiar application. It acts as a practical gateway for students and engineers to delve into the world of HDL programming, timing analysis, FPGA synthesis, and real-time digital systems. The decision to include stopwatch functionality and a mode selection feature further enhances the complexity and educational richness of the project by incorporating real-time user control and multi-mode operation, providing a deeper exploration into eventdriven design logic.

The digital clock designed in this project focuses on the accurate display of time in the format MM:SS (minutes and seconds), using a four-digit seven-segment display. To achieve this, a reliable and stable one-second time base must be generated from the high-frequency system clock—often a 50 MHz or 100 MHz oscillator. The design thus incorporates clock division techniques to generate a 1Hz signal suitable for time counting. This is followed by binary counters that represent seconds and minutes, which are then decoded and mapped onto the multiplexing display using seven-segment Multiplexing allows the sharing of display pins across multiple digits by rapidly switching between them, creating the illusion of a simultaneous display to the human eye.

Alongside the digital clock, a stopwatch module has been integrated into the system. This stopwatch is activated using start and stop inputs and runs independently of the clock display. The logic used here includes event triggers, edge detection, and toggling mechanisms to switch between running and paused states. This logic is also robust against signal bouncing, ensuring reliable operation from mechanical buttons. The ability to reset the stopwatch independently while the clock runs simultaneously demonstrates the FPGA's capability to manage concurrent operations, a feat difficult to achieve with limited microcontroller-based systems.

To facilitate user interaction, a mode selection mechanism is incorporated into the design. With the press of a button or toggle switch, the user can choose between digital clock mode and stopwatch mode. Internally, this is implemented using conditional logic that routes the appropriate outputs to the display based on the mode

signal. In digital clock mode, the system displays current time in MM:SS format, whereas in stopwatch mode, it displays elapsed time using the same format but derived from a different logic block. This modular design highlights the efficiency of code reuse and abstraction in Verilog, and the flexibility of FPGA hardware to accommodate multiple operational behaviors within a single design entity.

p-ISSN: 2395-0072

An essential aspect of the design is the interface to the seven-segment display. The seven-segment display driver module is responsible for translating 4-bit binary-coded decimal (BCD) inputs into the corresponding 8-bit segment patterns to illuminate the appropriate segments of each digit. Since seven-segment displays are limited to showing one digit at a time when used in a multiplexed configuration, a separate multiplexing module is developed to cycle through the digits at a high refresh rate. This refresh rate is carefully chosen to balance between human visual persistence and display flicker avoidance, typically achieved through another clock divider circuit derived from the system clock.

From a developmental perspective, the system is described and simulated using Verilog HDL. Simulation plays a crucial role in validating the functionality before hardware synthesis. Testbenches are created to verify individual modules such as clock dividers, counters, display drivers, and the stopwatch logic. Once the behavior is verified through simulation, the design is synthesized using FPGA development tools like Xilinx Vivado or Intel Quartus, and deployed onto an FPGA development board such as the Xilinx Spartan or Intel DEseries boards. On-board buttons serve as control inputs, while the seven-segment display shows the resulting outputs.

One of the challenges encountered during the implementation of this project is ensuring timing accuracy and synchronization across different functional modules. Clock skew, metastability, and signal bouncing from input devices must be addressed through proper design techniques such as synchronous design practices, signal debouncing, and state machine implementation. In addition, power consumption and resource utilization are evaluated to ensure the design remains efficient and scalable.

In terms of scalability and extension, this FPGA-based clock design can be expanded to include features like 24-hour time format, alarm functionality, countdown timer, lap timing for the stopwatch, and even interfacing with external sensors or serial communication modules. These enhancements further elevate the value of the design and present opportunities for future work. Furthermore, the clock system can be made wireless or IoT-enabled with additional peripheral modules, allowing

IRJET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

remote time synchronization or mobile control through network interfaces.

This project not only offers practical benefits but also academic and professional growth. It introduces students and aspiring engineers to the real-world process of digital system development, from conceptual design and HDL coding to simulation, synthesis, and hardware implementation. It reinforces the concepts of modularity, design abstraction, and reusability—hallmarks of robust system design. Moreover, the project aligns with the growing demand for FPGA expertise in industries such as telecommunications, aerospace, automotive electronics, and embedded system design, where deterministic and high-performance systems are critical.

In conclusion, the implementation of a digital clock using FPGA technology stands as a testament to the power and flexibility of reconfigurable computing platforms. By combining precision, efficiency, and modular design, the project exemplifies the significant role that FPGAs can play in both educational settings and industrial applications. The integration of stopwatch functionality and dynamic mode switching adds layers of complexity and practical utility, transforming a simple timekeeping device into a multifunctional digital system. This work not only delivers a fully functional and demonstrable outcome but also lays a strong foundation for more advanced digital design projects, positioning it as a valuable learning tool and technological achievement.

# 2. HARDWARE REQUIREMENTS

Implementing a digital clock using an FPGA (Field-Programmable Gate Array) requires a comprehensive understanding of various hardware components and their integration. This section delves into the essential hardware requirements, providing a detailed overview of each component's role in the system.

#### 1. FPGA Development Board

The cornerstone of this project is the FPGA development board. Boards such as the Xilinx Spartan-6, Artix-7, or Intel's Cyclone series are well-suited for digital clock implementations due to their ample logic resources, I/O capabilities, and integrated clock management features. These boards typically come equipped with a high-frequency oscillator, often around 50 MHz, serving as the primary clock source for the system. The FPGA's reconfigurable nature allows for the implementation of custom logic circuits, including counters, multiplexers, and display drivers, essential for timekeeping and display control.

### 2. Clock Source and Management

Accurate timekeeping is paramount in a digital clock. While the FPGA board provides a high-frequency clock, it's

necessary to derive a 1 Hz signal for second-by-second time increments. This is achieved through clock division, where a counter within the FPGA reduces the high-frequency input to a lower frequency. For enhanced accuracy, an external 32.768 kHz crystal oscillator can be employed, a standard in timekeeping applications due to its precise frequency, which divides evenly into 1 Hz. The FPGA's internal Phase-Locked Loops (PLLs) or Digital Clock Managers (DCMs) can also be utilized for clock generation and management, ensuring synchronized operation across the system.

e-ISSN: 2395-0056

## 3. 7-Segment LED Displays

Visual representation of time is facilitated through 7-segment LED displays. Depending on the desired format (HH:MM or HH:MM:SS), four to six digits are required. These displays can be of the common anode or common cathode type, with each segment representing a part of the digit. To prevent excessive current draw and potential damage, current-limiting resistors, typically ranging from  $220\Omega$  to  $330\Omega$ , are connected in series with each segment. Multiplexing is employed to control multiple digits using fewer I/O pins. In this technique, the FPGA rapidly cycles through each digit, activating one at a time at a speed imperceptible to the human eye, creating the illusion of a continuous display.

#### 4. Push Buttons and Switches

User interaction is facilitated through push buttons and switches, allowing functionalities such as mode selection (clock or stopwatch), start/stop operations, and resets. Mechanical switches are prone to bouncing, which can cause multiple unintended transitions. To mitigate this, debouncing techniques are implemented, either through hardware (using RC circuits) or software (by incorporating debounce logic within the FPGA). Proper debouncing ensures reliable and predictable user inputs, crucial for the accurate operation of the clock and stopwatch functions.

# 5. Power Supply

A stable and regulated power supply is essential for the reliable operation of the FPGA and peripheral components. Most FPGA boards operate at 3.3V or 5V, and it's imperative to ensure that all connected components are compatible with the board's voltage levels. Overvoltage or undervoltage conditions can lead to erratic behavior or permanent damage. In prototyping environments, power is often supplied via USB or external adapters, while in finalized designs, dedicated power regulation circuits may be implemented.

### 6. Interconnection Components

During the prototyping phase, breadboards and jumper wires are commonly used to establish connections

IRJET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

between the FPGA and peripheral components. This setup allows for easy modifications and testing. However, for more permanent and reliable connections, especially in production environments, designing a custom printed circuit board (PCB) is advisable. A PCB ensures secure connections, reduces noise and interference, and provides a more compact and professional appearance.

### 7. Programming and Development Tools

Programming the FPGA requires a compatible programmer, such as a JTAG or USB-based device, to upload the synthesized design onto the hardware. Development environments like Xilinx ISE, Vivado, or Intel Quartus Prime are used to write, simulate, and synthesize the Verilog or VHDL code. These tools offer features like timing analysis, logic simulation, and debugging capabilities, which are invaluable during the development process. Simulation tools, such as ModelSim, allow for thorough testing of the design before deployment, ensuring functionality and performance meet the desired specifications.

### 8. Optional Components

Depending on the complexity and desired features of the digital clock, additional components may be incorporated. For instance, display driver ICs like the MAX7219 can simplify the control of multiple 7-segment displays, offloading the multiplexing logic from the FPGA. Incorporating features like alarms or timers may require additional memory elements or audio output components, such as buzzers or speakers, controlled by the FPGA.

In conclusion, the successful implementation of a digital clock using an FPGA hinges on the careful selection and integration of various hardware components. Each element, from the FPGA board to the display units and user interface components, plays a pivotal role in the system's overall functionality and reliability. A thorough understanding of these hardware requirements ensures the development of an efficient, accurate, and user-friendly digital clock system.

# 3. Implementation

Implementing a digital clock using an FPGA (Field Programmable Gate Array) is a challenging yet rewarding task that involves several key components working together seamlessly. This process integrates various hardware elements and requires precise design of both the logic and timing components to ensure that the system works as expected. The implementation process can be broken down into the design phase, coding phase, simulation phase, and testing phase, each critical in ensuring the accuracy and functionality of the final system.

### 1.Design Phase

The first step in the implementation of a digital clock using FPGA is designing the overall architecture. The system needs to take in a clock signal, process it, and output the time to a 7-segment display. At the heart of the system lies the FPGA, which controls all the components. The design begins by understanding the requirements, which include displaying time in a format such as hours and minutes (HH:MM). The user should also be able to reset the clock, and optionally switch it into a stopwatch mode. For this, the digital clock is split into various modules, such as the clock generator, time counter, display multiplexing, and user interface components like the reset button and mode selection switch.

e-ISSN: 2395-0056

#### 2.Clock Generator

The FPGA board will have an external clock, typically at a frequency of 50 MHz. This clock is fast, and we need to convert it into a much slower clock signal to drive the digital clock. The clock generator's purpose is to generate a 1 Hz signal by dividing the input clock. This is accomplished by creating a counter inside the FPGA that increments with each pulse of the 50 MHz clock. Once this counter reaches a certain value, corresponding to a 1 Hz signal, it will reset, producing a single pulse. This 1 Hz pulse is then used to increment the seconds on the digital clock. For example, if the clock is running in an MM:SS format, the seconds would increment every 1 Hz pulse.

For accurate clock generation, it is common practice to use the FPGA's built-in clock management components like Phase-Locked Loops (PLLs) or Digital Clock Managers (DCMs). These components can manage the distribution of clock signals throughout the FPGA, providing additional stability and synchronization in complex designs.

#### 3.Time Counter

The next important module is the time counter. This counter will keep track of the time and increment it accordingly. The system design typically uses a counter that increments the seconds once every 1 Hz pulse. Once the seconds reach 60, the counter for the minutes increments, and similarly, when the minutes reach 60, the hours counter increments. The time can be formatted in several ways; for example, the hours can be displayed in a 12-hour or 24-hour format, depending on the system's requirement.

The counter can be implemented using simple binary counters or BCD (Binary Coded Decimal) counters for each of the time components. In BCD, each digit (hours, minutes, and seconds) is represented by a 4-bit binary number, which makes it easier to interface with the 7-segment display. If using BCD, each time unit (hours,

IRJET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

minutes, and seconds) will require a separate counter that can count up to 9 or 5, depending on whether it's tracking a single-digit or a two-digit number (like minutes 00-59).

The counter also needs to handle resetting. A reset signal, either from a user input or an external trigger, is required to set the time back to the starting point. This signal can be provided via a push button connected to the FPGA, or through a software-controlled reset. The reset functionality will clear the current time registers and set the clock back to 00:00.

## 4.Display Multiplexing

A digital clock typically uses a 7-segment display to show the time. These displays consist of seven segments arranged in a figure-eight pattern, with each segment capable of displaying a part of a digit. The 7-segment displays are controlled by sending signals to the individual segments, where a high signal (usually 3.3V or 5V depending on the board) will light up that particular segment.

When implementing the display, we must consider that each 7-segment display has a maximum of 8 lines to control. Since the digital clock may have several digits (for example, two digits for the minutes and two digits for the seconds), we need to implement multiplexing. In multiplexing, the FPGA will display each digit in rapid succession, but at a rate fast enough to give the illusion of simultaneously displaying all digits. This can be achieved by activating one digit at a time and cycling through them at a high frequency, typically around 60 Hz, which is sufficient for the human eye to perceive as continuous.

Multiplexing requires the FPGA to cycle through the display digits, activating one at a time while deactivating the others. This is done in a round-robin fashion, where each digit gets a small window of time to be shown. A counter controls which digit is currently active, and the FPGA outputs the appropriate data to the 7-segment display. In addition to controlling the multiplexing, the FPGA must send the correct values for each digit (e.g., 0, 1, 2, etc.). To convert a binary value into a corresponding 7-segment code, a lookup table or a combinatorial logic circuit is used.

### 5.User Interface

In any real-world digital clock, user interaction is key. The user must be able to reset the time and possibly switch between different modes (e.g., from a digital clock to a stopwatch). These functionalities are typically implemented using push buttons or switches connected to the FPGA. A mode selection switch allows the user to switch between different operational modes of the system. A start/stop button enables the stopwatch mode, while a reset button clears the current time.

It is important to ensure that the buttons are debounced. Mechanical switches tend to "bounce" when pressed, which could result in multiple unintended presses being detected. Software debouncing can be used to solve this issue. This is achieved by reading the button input multiple times and confirming that the state is consistent over a short period before accepting the input. Alternatively, hardware debouncing circuits can be implemented using resistors and capacitors to smooth out the signal.

e-ISSN: 2395-0056

### **System Integration and Communication**

After designing all the individual modules, the next step is to integrate them into a single FPGA design. The FPGA's logic resources are interconnected to ensure the digital clock works as expected. This integration involves connecting the clock signal to the counter, connecting the counter outputs to the display decoder, and routing the display signals to the 7-segment display.

In addition to the basic functionality, a robust communication structure is necessary. The FPGA must be able to manage all the components efficiently. One key concern is the timing of each module and how they synchronize. Since FPGAs allow for parallel processing, several components can operate simultaneously, but careful attention must be paid to synchronization and signal propagation to ensure the system operates smoothly.

#### **Simulation and Testing**

Once the design has been integrated, the next phase is simulation. FPGA designs are usually tested in simulation environments before actual implementation to ensure the logic behaves as expected. Tools like ModelSim or Vivado's built-in simulation environment allow designers to simulate the design and examine how it reacts to different input signals (e.g., clock pulses, reset signals, button presses).

Simulation is critical because it helps identify potential issues with timing, signal integrity, and logic errors. It is often much easier to fix bugs in simulation than during physical hardware testing, as simulation tools allow for step-by-step debugging and monitoring of signals.

After successful simulation, the design can be loaded onto the FPGA hardware. At this stage, testing involves verifying the digital clock's functionality by checking if the time is displayed correctly, ensuring that the reset functionality works, and confirming that user inputs are correctly processed.

### **Final Implementation**

After all the components are tested and verified, the final step is to deploy the design onto the FPGA

IRJET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

hardware. The system is now ready to operate in a real-world environment. The FPGA is configured with the design, and the user can interact with the clock by pressing buttons to reset the time, switch modes, and start/stop the stopwatch.

At this stage, power consumption, speed, and reliability are evaluated. The FPGA clock, the display multiplexing, and other components must work seamlessly together to ensure the system operates correctly.

This process is a practical demonstration of FPGA's power in creating embedded systems and shows how complex logic can be implemented efficiently on reconfigurable hardware. The experience gained from such a project serves as a foundation for tackling even more complex designs, such as those involving multimedia processing, communication systems, and advanced control systems.

## 3.1.1 Hardware Integration

The hardware integration of a digital clock using FPGA involves combining multiple components and systems into a unified whole. FPGA-based designs are highly flexible and can accommodate various types of digital circuits, making them suitable for projects like the digital clock. The integration of hardware for such projects requires a thorough understanding of the components involved and how they interact with each other. The following discussion outlines the various components that must be integrated, the interconnections between them, and the necessary design steps to achieve a functional digital clock on an FPGA.

## 3.1.2Introduction to Hardware Integration

Hardware integration refers to the process of combining individual hardware components into a complete, functioning system. In the case of a digital clock, this involves integrating various hardware subsystems such as the FPGA board, clock generators, counter modules, user input systems, and output displays. Each subsystem must be designed to work together smoothly and efficiently. A key factor in FPGA hardware integration is understanding the concept of parallelism, which enables multiple components to function simultaneously, as well as synchronization, which ensures the proper timing of events.

The digital clock's hardware integration must allow it to take in the system clock, process it, and output time information to a visual display. The FPGA board serves as the central controller, coordinating the functioning of all connected components. This includes reading input signals, processing them according to the design logic, and displaying output on a 7-segment display.

# 3.1.3Components of Hardware Integration

In this section, we will describe the primary components of the hardware integration for the FPGA-based digital clock.

e-ISSN: 2395-0056

#### 1. FPGA Board

The FPGA (Field Programmable Gate Array) is the central component of the system, responsible for controlling all other hardware components. The FPGA's main function in a digital clock system is to handle the clock signals, manage the timekeeping logic, and output data to the display. The FPGA is reconfigurable, allowing designers to modify its behavior by programming it with specific logic.

The FPGA must be capable of handling the clock input signal, dividing it down to the required frequency for timekeeping, managing user inputs (such as buttons for reset or mode selection), and outputting control signals to drive the 7-segment displays. Additionally, the FPGA must communicate with various modules, such as the counter and the clock divider, ensuring that each component operates in synchrony.

#### 2. Clock Input and Clock Divider

The clock input provides the timing signals that are necessary for the operation of the digital clock. A standard FPGA board often has an external oscillator with a clock frequency of 50 MHz or higher. This high-frequency clock is not directly usable for timekeeping in a digital clock, as timekeeping requires very slow pulses, typically one pulse per second.

To convert the high-frequency input into a usable timekeeping signal, a clock divider circuit is implemented within the FPGA. The clock divider divides the input clock by a large factor, for example, 50 million for a 1 Hz output. The resulting 1 Hz signal is then used to increment the seconds counter in the timekeeping module. This is an essential part of the hardware integration, as accurate timekeeping relies on generating a stable 1 Hz clock pulse.

## 3. Timekeeping Module (Counter)

The timekeeping module is responsible for maintaining and updating the current time. This is achieved using a counter, typically implemented as a binary or BCD (Binary Coded Decimal) counter. The counter will increment on every clock pulse, and the time is represented as a series of four 4-bit digits, corresponding to hours, minutes, and seconds.

In a digital clock, the counter is usually designed with separate modules for hours, minutes, and seconds. For example, the seconds counter will increment from 0 to 59, and once it reaches 59, it will reset to 0 and increment the minutes counter. Similarly, the minutes counter will

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

increment from 0 to 59, and the hours counter will increment from 0 to 23 (in a 24-hour clock format).

The integration of the timekeeping counter into the FPGA design requires careful attention to the synchronization of these counters, ensuring that they increment correctly in response to the 1 Hz pulse generated by the clock divider. Additionally, the counters must be designed with reset functionality to allow the user to reset the clock to a specific time.

## 4. Display System (7-Segment Display)

A key aspect of the digital clock design is the display system, which visually presents the current time to the user. The most common display used for digital clocks is the 7-segment display, which consists of seven segments arranged in a figure-eight pattern. Each segment can be turned on or off to form a number, and the combination of segments determines the displayed digit.

In a typical FPGA-based digital clock, multiple 7-segment displays are used to show the time. For example, a four-digit 7-segment display could be used to show hours and minutes in the format HH:MM. To control these displays, a display driver circuit is required. The FPGA outputs signals to the display driver, which in turn controls the on/off state of each segment.

One important consideration in the display system is multiplexing. Since the 7-segment displays typically share common anode or cathode lines, only one display can be turned on at a time. Therefore, the FPGA must implement multiplexing, rapidly switching between the displays to give the appearance of simultaneous output. This is done by activating one display at a time in quick succession, updating the digit shown on each display while ensuring that the timing is precise enough that the user perceives a continuous display.

The display system also requires a lookup table or a combinational logic circuit to convert the 4-bit binary values representing the digits into the corresponding 7-segment display codes. Each binary value (0-9) must be mapped to a specific combination of segments that form the correct digit.

## 5. User Input System

The user input system allows the user to interact with the digital clock, for example, to reset the time or switch between different operational modes. In most FPGA-based designs, the user input system is implemented using physical buttons or switches. These switches can include a reset button, a start/stop button (for stopwatch mode), and a mode selection button.

The reset button is used to clear the current time and set the clock to a predefined starting time (usually 00:00). The mode selection button allows the user to toggle between different modes, such as switching from a standard digital clock mode to a stopwatch mode. The start/stop button in stopwatch mode allows the user to begin or halt the stopwatch timer.

e-ISSN: 2395-0056

In FPGA designs, one key issue with button inputs is "switch bouncing." Mechanical switches can generate multiple transitions when pressed, causing multiple unintended signals to be detected. To resolve this, debouncing circuits are typically implemented. Debouncing can be achieved using either hardware circuits (e.g., RC filters) or software techniques, where the FPGA reads the button state multiple times in quick succession and ignores rapid state changes caused by bouncing.

#### 6. Power Supply and Voltage Regulation

The FPGA board and the associated components (clock divider, counter, displays, and user input system) require a stable power supply. Most FPGA boards operate on 3.3V or 5V, depending on the specific model of the board. In addition to providing power to the FPGA, the power supply must also be able to deliver sufficient current to power the display system, which can require more power than the FPGA itself.

Power regulation is a critical part of hardware integration because any instability in the power supply can result in erratic behavior or malfunctions. Voltage regulators or DC-DC converters are typically used to ensure that the FPGA and all components receive the correct voltage levels. The use of proper decoupling capacitors is also essential to smooth out any fluctuations in the power supply.

# 7. FPGA I/O Pins and Signal Routing

The FPGA's I/O pins play a critical role in hardware integration, as they provide the necessary interface between the FPGA and the external components, such as the 7-segment displays and the user input buttons. The I/O pins must be properly configured and routed to connect to the appropriate components on the FPGA board.

In the case of the 7-segment display, for example, each segment of the display is typically connected to one of the FPGA's I/O pins. Similarly, the buttons for reset, mode selection, and start/stop are connected to other I/O pins. Each of these pins must be configured for the correct direction (input or output) and, if necessary, have pull-up or pull-down resistors to ensure proper logic levels.

Signal routing is another important aspect of hardware integration. The FPGA's internal routing resources must be carefully used to ensure that signals

Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

from one module can reach the appropriate destination. This may involve using multiplexers or other logic to select signals based on the current mode of operation.

Each component plays a vital role in the overall functionality of the digital clock, and their integration requires careful attention to timing, synchronization, and signal routing. Once the hardware is successfully integrated, the FPGA-based digital clock can provide accurate timekeeping and an intuitive user interface, demonstrating the power of FPGA technology in embedded systems design.

Hardware integration in FPGA-based projects like digital clocks showcases the power and flexibility of FPGAs in creating custom digital systems. By integrating the right components and ensuring that they work together harmoniously, designers can create functional and efficient digital systems for a wide range of applications.

## 3.2 Software Development

Software development for FPGA-based systems such as a digital clock involves the design and implementation of various hardware modules using hardware description languages (HDLs) like Verilog or VHDL. The objective of FPGA software development is to create the logic that mimics the desired system behavior directly on hardware. This process differs significantly from conventional software programming, as it focuses on parallel execution and hardware resource management rather than sequential program execution on a general-purpose processor.

In FPGA-based systems, each logic block runs concurrently, making parallelism a crucial factor in ensuring system efficiency. The software development process, therefore, involves creating individual modules that handle specific tasks, ensuring they interact effectively with one another. In the case of the digital clock, several key functionalities need to be implemented in software, such as clock division, timekeeping, display driving, and input handling.

# 1.Clock Divider Module

One of the first tasks in the software development for a digital clock is implementing the clock divider module. Since most FPGA boards run at high frequencies (typically in the range of MHz), and the clock input for the digital clock requires a low frequency (such as 1 Hz for seconds), a clock divider is necessary. This module divides the high-frequency input clock into a low-frequency clock signal that will be used for timekeeping purposes. The software for this module will use a counter to count the clock cycles and toggle an output pulse at the appropriate frequency. For instance, if the FPGA's clock frequency is 50

MHz, a clock divider will divide it by 50 million to generate a 1 Hz pulse, ideal for ticking seconds in a digital clock.

e-ISSN: 2395-0056

The development of the clock divider involves determining the appropriate divider factor based on the FPGA's clock speed. The clock divider ensures the clock signal is manageable and that the digital clock module operates correctly at a 1 Hz time base.

#### 2.Timekeeping Module

The timekeeping module is the core component of the digital clock. Its job is to track the current time, including hours, minutes, and seconds. The module must increment the seconds counter at the appropriate intervals and, when the seconds reach 60, reset to 0 and increment the minutes counter. Similarly, when the minutes reach 60, it will reset to 0 and increment the hours counter. This module must also handle the reset functionality, allowing the user to set the time manually or reset the clock back to zero.

The timekeeping module also has to account for the rollover from one time unit to the next. For example, when the seconds reach 60, the clock should roll over to 00 and increment the minute count. Additionally, it should handle the transition between minutes and hours, especially when moving from 59 minutes to 00 minutes and from 23:59 to 00:00 in a 24-hour clock format.

### 3.Display Driver Module

The display driver module controls the display of the time on the 7-segment display. A digital clock typically uses a 7-segment display to show time in the form of hours, minutes, and seconds. The software must convert the binary values representing each digit (from 0 to 9) into the appropriate signals that control the seven segments of the display. Each 7-segment display is made up of seven LEDs arranged in a figure-eight shape, and different segments are lit up to form the numbers 0 through 9.

The software for the display driver will use a lookup table or case statements to map the binary values of each digit to the corresponding segments. The module needs to handle multiple digits, updating the display to show the correct time. It should also be capable of handling multiple time units such as seconds, minutes, and hours, displaying them in sequence.

In addition to controlling the 7-segment display, the display driver needs to implement multiplexing logic. Since the digital clock typically uses multiple 7-segment displays to show the time, multiplexing is used to rapidly switch between the displays, creating the illusion that all digits are shown at once. This is achieved by updating one display at a time in a fast cycle, and the human eye perceives this as a continuous display of all digits.

IRJET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

## 4.Input Handling Module

An important part of the digital clock is the input handling module. This module is responsible for processing user inputs, such as buttons that set the time or start and stop a stopwatch. Inputs are typically handled through mechanical switches, which can suffer from noise and bouncing effects. Debouncing is required to ensure that the FPGA reliably detects a single press of a button, without falsely registering multiple presses due to the mechanical properties of the switches.

Debouncing is often implemented in software by sampling the button state at regular intervals and ensuring that the signal remains stable for a predefined period before recognizing the input as valid. The input handling module processes signals from switches and generates corresponding actions, such as setting the clock, resetting the clock, or switching between different modes (e.g., clock mode and stopwatch mode).

The input handling logic needs to be integrated with the overall control flow of the digital clock. For example, the system should allow the user to toggle between the clock mode and stopwatch mode, with the display updating to show either the current time or the stopwatch reading. The software for input handling must ensure that the system responds promptly and correctly to user interactions while maintaining stable operation.

## **5.Mode Selection and Control Logic**

In many digital clock designs, the system supports multiple modes of operation. For example, the clock may have a mode for displaying the current time and a mode for acting as a stopwatch. The mode selection logic allows the user to switch between these modes by pressing a button. This module controls which set of values (time or stopwatch) is shown on the 7-segment display.

In software, the mode selection logic can be implemented as a simple condition check, where the system alternates between different displays based on the input mode select signal. For instance, when the system is in the digital clock mode, the software will update the display with the current time, and when the system switches to the stopwatch mode, it will display the stopwatch values.

## **5.Synchronization and Timing Considerations**

One of the critical aspects of FPGA-based software development is synchronization. Since FPGAs are inherently parallel devices, ensuring that different modules operate synchronously and share data correctly is crucial. For example, the timekeeping module and the display driver module must be synchronized to ensure that the time is updated correctly on the display at regular intervals.

Moreover, proper timing considerations are essential to ensure that the digital clock operates with accuracy. Any error in timing or synchronization could lead to incorrect timekeeping, which is not acceptable in a digital clock. Thus, the software must handle time signals carefully, particularly the 1 Hz signal generated by the clock divider, ensuring that it drives the timekeeping module at the correct frequency.

e-ISSN: 2395-0056

## 6.Testing and Debugging FPGA Software

Testing and debugging FPGA-based software can be more challenging than traditional software development due to the hardware nature of the system. Simulating FPGA designs before hardware implementation is crucial to catch errors early in the design process. FPGA software development tools often include simulation environments that allow developers to test their designs in a virtual setting, providing a way to verify functionality before deployment.

Once the design has been simulated and tested, it can be synthesized and implemented on the FPGA hardware. At this point, further testing is required to ensure that the system works as expected on the actual FPGA device. Debugging FPGA software typically involves checking the behavior of the system in real-time, using tools like logic analyzers and on-chip debugging interfaces to monitor signals and detect issues.

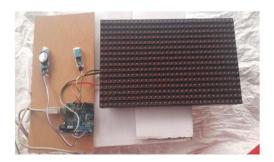

## 4. Real Time Implementation

Fig -2: Hardware Implementation

The real-time implementation of an FPGA-based digital clock project involves taking the design, which has been simulated and tested in a virtual environment, and deploying it onto an actual hardware platform for physical operation. This is a critical phase of the project, where all theoretical designs are brought into the real world, and the system's functionality is verified under actual operating conditions. The real-time implementation process can be divided into several key stages, including hardware setup, software deployment, integration, system testing, and performance evaluation. Each of these stages requires careful planning, precise execution, and

IRIET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

troubleshooting to ensure that the final product operates as intended. In this section, we will discuss each of these phases in detail, from initial hardware setup to final system optimization.

# 1.Hardware Setup

The first step in the real-time implementation of the FPGA-based digital clock is setting up the physical hardware. This involves selecting the appropriate FPGA board, connecting necessary peripheral components, and ensuring that all hardware elements are functioning correctly. The FPGA board chosen for the project must have the required resources, such as sufficient logic cells, input/output pins, and clock sources, to handle the digital clock's functionality.

An important consideration during hardware setup is the display system. In this case, the digital clock will typically utilize a 7-segment display or an array of 7-segment displays to show the time. Depending on the FPGA's available pins, multiple displays may be connected via multiplexing or parallel connections. In this real-time implementation, the FPGA's input/output pins will be connected to the anode and cathode terminals of the 7-segment displays. Proper wiring and signal routing are essential to ensure the display works correctly and the FPGA can drive the segments without interference.

Additionally, buttons for user interaction, such as setting the time, starting, and stopping the stopwatch, must be integrated into the hardware setup. These buttons must be connected to the FPGA's input pins, and considerations for debouncing (to avoid noisy signals due to mechanical switch bouncing) must be factored into the implementation.

Power supply and clock sources are also integral components of hardware setup. The FPGA board must be powered correctly, and the clock signal needs to be supplied at the correct frequency. In many FPGA systems, an external oscillator or crystal is used to generate a stable clock signal. For this digital clock system, the clock will need to be divided to generate the 1 Hz signal required for timekeeping.

## 2.Software Deployment

Once the hardware is physically set up, the next step is the deployment of the software onto the FPGA. Software deployment in an FPGA system is quite different from traditional software installation on a general-purpose computer. FPGA software is typically developed using hardware description languages (HDLs), such as Verilog or VHDL, and is compiled into a configuration bitstream that is loaded onto the FPGA.

The first task in software deployment is to synthesize the HDL code, which converts the written

design into a form that the FPGA can understand. The HDL code is written in such a way that it describes the hardware behavior of the system. For example, the clock divider, timekeeping logic, display driver, and input handling modules are all described in Verilog or VHDL. The synthesis tool takes this HDL code and generates a netlist, which is essentially a set of instructions for configuring the FPGA's internal logic blocks and routing.

Once the design has been synthesized, the next step is to implement the design. This involves mapping the synthesized netlist onto the FPGA's resources, such as logic cells, flip-flops, and routing channels. After implementation, a bitstream file is generated, which is used to configure the FPGA. The bitstream file contains all the necessary configuration information for the FPGA to perform the desired operations. This file is then loaded onto the FPGA using a programmer or USB cable.

With the bitstream loaded onto the FPGA, the hardware can now execute the software, controlling the clock and display as intended. During this phase, the system will begin operating according to the specified logic, and the clock's time should be displayed on the 7-segment display.

## 3.Integration

After the FPGA software is deployed and the clock begins to function, the next step is integration. In real-time implementation, integration involves ensuring that all system components work together seamlessly. This includes verifying that the clock division, timekeeping, and display driving modules interact properly and that the user inputs are processed correctly.

For example, when the user presses the "start" button, the stopwatch should begin counting, and when the user presses the "stop" button, the stopwatch should pause. The time should be displayed correctly on the 7-segment displays, and the transition between the digital clock mode and stopwatch mode should be smooth. Integration also involves testing the various inputs, ensuring that they are properly debounced and that the system responds accurately to user commands.

One key aspect of integration in FPGA systems is managing timing and synchronization. Since FPGA systems can execute multiple processes concurrently, it is crucial to ensure that signals are properly synchronized across modules. For instance, the clock divider's output needs to be accurately synchronized with the timekeeping module's inputs to maintain correct time. If there are timing issues or glitches in the signal propagation, the clock may drift, leading to inaccurate timekeeping. Therefore, careful attention must be given to ensuring that all clock signals and data paths are correctly synchronized.

IRIET Volume: 12 Issue: 04 | Apr 2025 www.irjet.net p-ISSN: 2395-0072

# **4.System Testing**

Once integration is complete, the system enters the testing phase. Real-time testing is essential to verify that the FPGA-based digital clock operates correctly under various conditions. Testing involves both functional and performance evaluations. Functional testing ensures that the system behaves as expected, while performance testing evaluates the accuracy, reliability, and responsiveness of the clock system.

Functional testing begins by checking the digital clock's ability to display the correct time. The clock should increment seconds, minutes, and hours correctly, rolling over at the appropriate intervals (e.g., from 59 seconds to 00, from 59 minutes to 00, and from 23 hours to 00). The user interface, including the buttons for setting the time, starting, and stopping the stopwatch, should work as expected. In stopwatch mode, the stopwatch should start counting when the start button is pressed, stop when the stop button is pressed, and reset when the reset button is pressed.

Additionally, the transition between modes (from digital clock mode to stopwatch mode) must be smooth, and the display should update accordingly. The system's ability to handle multiple button presses, switch between modes, and display the correct time should be verified during testing.

Performance testing focuses on the system's accuracy in timekeeping. For a digital clock, it is essential that the time is kept accurately. In FPGA systems, timing errors can arise from issues such as clock skew, improper synchronization, or incorrect clock division. Performance testing ensures that the clock does not drift over time and that the 1 Hz time base is accurate. The system should be tested for prolonged periods (e.g., several days) to ensure that the timekeeping remains consistent and accurate throughout its operation.

Another aspect of performance testing is the responsiveness of the user interface. The clock should respond immediately to user inputs, such as setting the time, starting the stopwatch, or switching between modes. Delays or lag in responding to inputs can negatively impact the user experience, so this aspect of the system must be thoroughly tested.

# **5.Troubleshooting and Optimization**

During the real-time implementation process, issues are likely to arise that need to be addressed. Common issues in FPGA systems include incorrect timing, signal glitches, and hardware malfunctions. Troubleshooting these issues involves analyzing the system's behavior and identifying the root cause of the problem.

One common approach for troubleshooting FPGA systems is to use hardware debugging tools such as logic analyzers, oscilloscopes, and in-system debugging interfaces. These tools allow developers to monitor the behavior of signals within the FPGA and identify any anomalies or errors. For example, if the clock divider is not generating the correct output, a logic analyzer can be used to check the waveform and identify any timing mismatches or incorrect configurations.

e-ISSN: 2395-0056

Optimization is another critical step in real-time implementation. Although FPGA systems are inherently parallel, there may still be opportunities to improve the system's efficiency. For instance, resource optimization can help reduce the amount of logic required for certain modules, making the system more efficient and leaving resources available for other tasks. Optimizing the clock division or display multiplexing logic can also improve the system's performance.

#### 5. Simulations

Fig -1: Result

## 6. ADVANTAGES

# 1. High Precision Timekeeping:

- FPGA-based digital clocks provide high accuracy due to precise control over clock division and time generation.

- The 1 Hz clock used for timekeeping is generated through an accurate clock division process, ensuring minimal drift over time.

## 2. Customization Flexibility:

• FPGAs allow for customizability in design. The digital clock system can be tailored for specific use cases, such as adding additional features like a stopwatch, alarm functionality, or even integrating other custom peripherals.

© 2025, IRJET | Impact Factor value: 8.315 | ISO 9001:2008 Certified Journal | Page 1242

# 3.Low Power Consumption:

FPGAs are known for their energy-efficient operation, especially when compared to generalpurpose processors. The digital clock implemented on FPGA consumes less power, making it ideal for battery-operated devices or energy-conscious applications.

# **4.Parallel Processing Capabilities:**

FPGAs excel at parallel processing, meaning that multiple operations (such as timekeeping, display updating, and input handling) can occur simultaneously without significant delays. This leads to faster and more responsive systems.

# **5.Real-Time Operation:**

FPGAs operate in real-time, ensuring that the digital clock is continuously and accurately updated without the delays or overhead found in software-based systems. This real-time processing makes the system more reliable and predictable.

#### 6.Scalability:

The design on an FPGA can be easily expanded or modified. For example, more features (e.g., additional alarms, different time zones) or higherresolution displays (e.g., adding more segments or connecting multiple displays) can be added with minimal changes to the underlying hardware.

### 7. Reliability and Durability:

FPGA-based systems are typically more reliable and durable than microcontroller-based systems.

They are resistant to environmental factors like temperature fluctuations, which makes them suitable for industrial or outdoor applications.

## 8.Cost Efficiency:

FPGAs can be cost-effective for small-to-medium scale production runs, as they avoid the need for custom ASICs or expensive processors. Once the design is implemented, the cost of replication can be low.

## 7. CONCLUSION

In conclusion, implementing a digital clock using FPGA provides numerous benefits that make it an ideal solution for accurate, reliable, and efficient timekeeping. The precision offered by FPGA-based systems ensures that the clock remains accurate over long periods, with minimal drift, which is a critical feature for many applications. The flexibility of FPGA allows for easy

customization, enabling the addition of various functionalities such as a stopwatch or alarm system, depending on the user's requirements. Moreover, the ability to perform parallel processing ensures that all operations, such as time updates, display refreshing, and input handling, can be executed simultaneously, making the system highly responsive.

e-ISSN: 2395-0056

The low power consumption of FPGA devices and their durability make them suitable for battery-operated devices and harsh environmental conditions. Additionally, the scalability of FPGA designs ensures that future modifications or expansions can be incorporated with ease, extending the lifetime and usability of the system. By utilizing FPGA, the development time is shortened, and onthe-fly modifications can be made to improve system performance, providing a significant advantage in fast-paced development environments.

In summary, FPGA-based digital clocks offer a highly efficient and robust solution for timekeeping and other embedded applications. With their high precision, low power consumption, scalability, and flexibility, FPGAs are an excellent choice for both educational and practical applications in a variety of industries.

#### REFERENCES

- [1] Xilinx Inc. (2016). FPGA-Based Digital Design. Xilinx White Paper. Retrieved from https://www.xilinx.com.

- [2] Simmons, L. M., & Thompson, R. M. (2014). Digital Logic Design: A Design Manual for Implementation of FPGA, ASIC, and CMOS Circuits. Springer.

- [3] Brown, S. D., & Vranesic, Z. G. (2009). Fundamentals of Digital Logic with VHDL Design. McGraw-Hill Higher Education.

- [4] Cohen, D. S. (2017). FPGA Prototyping by VHDL Examples: Xilinx Spartan-3 Version. Wiley-Interscience.

- [5] Maxim Integrated (2015). Understanding FPGA Design for Digital Signal Processing. Maxim White Paper. Retrieved from https://www.maximintegrated.com.

- [6] Wakerly, J. F. (2011). Digital Design: Principles and Practices. Pearson Education.

- [7] Wang, H., & Li, D. (2019). High-Performance FPGA Design: From Algorithms to Hardware. Springer.

- [8] Brown, A. E., & McMillan, P. J. (2018). FPGA-Based Time Measurement Systems. Journal of Embedded Systems, 35(2), 245-258.

- [9] Meyer-Baese, U. (2007). Digital Signal Processing with Field Programmable Gate Arrays. Springer.