# **Implementation of Split Array Based Charge Scaling DAC**

### Sumangala.N<sup>1</sup>, Bharathi.S.H<sup>2</sup>

<sup>1</sup> M.Tech Student, Department of Electronics and Communication, Reva ITM, Karnataka, India. <sup>2</sup>Professor, Department of Electronics and Communication, Reva ITM, Karnataka, India.

\_\_\_\_\_

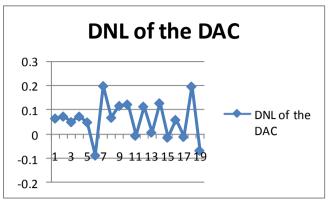

Abstract— This Paper presents the implementation of 6 bit split array based charge scaling DAC, with low power dissipation and less area. Proposed design is implemented in Cadence virtuoso tool using GPDK 180nm CMOS technology, with supply voltage of 1V. Split array based charge scaling DAC is employed in Successive Approximation register ADC or can be used as standalone device in wireless sensor network Transceivers. The output voltage swing provided by the DAC is -0.2mV to 0.93mV in steps of 14.6mV. The design has DNL error less than 0.5 LSB.

*Index Terms-* Two-stage op-amp, DAC, DNL, ICMR, low power, low area

#### **1.INTRODUCTION**

Data converters lie at the heart of modern Digital Signal Processing systems. The real time analog signals are to be converted to digital signals, due to ease of processing. Therefore, data converters are used as interface circuitry between digital and analog domain [1].

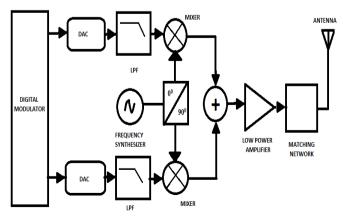

As the development of Radio Frequency (RF) communication assisted by progress in VLSI technology has made it practical to build high rate compactly packed digital circuit [2]. Figure (1) shows the application of converters in Wireless Sensor Network (WSN) transceiver system.

Figure 1: Direct conversion transmitter used in WSN transceiver

In WSN Transceivers, ADC converts the continuous signal to digital signal for processing. Once processing is done, DAC converts the digital signal to analog signal, which is then smoothened by Low Pass Filter and up-converted using mixer for wireless long distance communication.

#### 2. Proposed dac Architecture

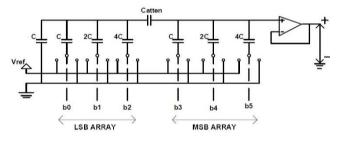

Charge scaling DAC with split array is presented in Figure (2) which decreases area and power by splitting the Binary Weighted Capacitor (BWC) array into two sub-arrays [3]. To make the total capacitance of the LSB array equal to the capacitance of the lowest bit in the MSB array, an attenuation capacitor with a fractional value is inserted. The result of the capacitor array is given to the op-amp to get the resultant analog signal.

Figure 2: Proposed DAC

### 2.1 Op-amp

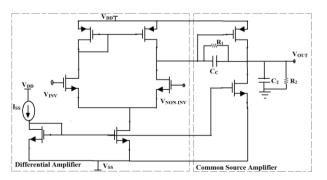

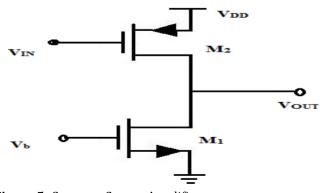

The Op-amp used in the proposed DAC architecture is the two stage op-amp as shown in Figure (3), the

Figure 3: Two Stage Op-amp

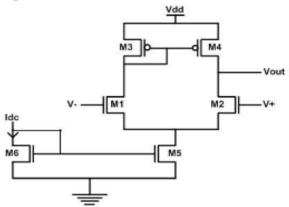

initial stage is the differential amplifier (In figure (4)) that yields high gain. Differential signals reject common mode noise, robust to supply noise, simpler biasing and has higher linearity. For extremely low common mode level the transistor  $M_1$  and  $M_2$  will turn off causing a severe clipping at the output.

Therefore the bias current should have least dependence on input common mode level. To solve this problem current source  $I_{SS}$  is used for  $I_{D1}$ -  $I_{D2}$  to be independent of input common mode level [4]. If  $V_{IN}$  is much more negative then  $M_1$  is OFF,  $M_2$  is ON.

If  $V_{IN-}$  increases  $M_1$  gradually turns ON , drawing a part of  $I_{SS}$  from  $R_{D1}$  and hence  $V_{OUT=}V_{DD} - (I_{SS}/2) R_D$  increases. As  $V_{IN-}$  becomes more positive  $M_1$  carries greater current than  $M_2$  and  $V_{OUT2}$  increases. For larger  $V_{IN-} - V_{IN+}$ ,  $M_1$  hogs all of  $I_{SS}$  turning  $M_2$  OFF, as a result  $V_{OUT} = V_{DD}$ .

Figure 4: Differential Amplifier

The second stage of Op-amp is the Common source amplifier shown in figure (5). The output swing and gain of differential amplifier is increased by using a common source amplifier. Load impedance of common source stage is increased to increase the gain. However increasing the output impedance limits the output voltage swing. Therefore, load of the common source stage is restored by a current source.

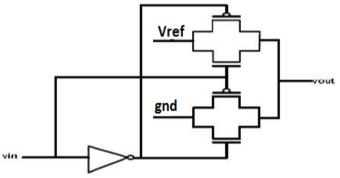

2:1 MUX SWITCH

2:1 multiplexer is employed as switch in proposed DAC. A multiplexer (MUX) is a switch that directs one of its inputs to the output. The input select signal decides which input to be moved to the output. Multiplexer is unidirectional. Multiplexer is used in application where input must be chosen from multiple data to a single output [5].

A 2:1 multiplexer requires an inverter and two Transmission gate (TG). The input select signal activates one of the TG. If  $V_{IN}$  is "logic 1",  $V_{REF}$  is passed to the output  $V_{OUT}$ . When  $V_{IN}$  is "logic 0", output is linked to gnd.

Figure 6: 2:1 MUX as Switch

# **3.Design of Digial to Analog Converter Archietecture**

Design of op-amp begins with the power budget [6]. Twostage Op-amp is designed by beginning with total power consumption of DAC to be  $500\mu$ W. So, Op-amp with power consumption in the order of few microwatts is to be designed. Beginning with this given power, and using supply voltage of 1V in 0.18 n-well CMOS technology, value of total current flowing through the op-amp is calculated.

Input transistors are designed so that maximum current flows through them, as the input transistors decide the gain of op-amp. Assuming overdrive voltage to be 0.2V, and using  $\mu_n C_{ox}$ =300 $\mu$ A/V<sup>2</sup> and  $\mu_p C_{ox}$ =60 $\mu$ A/V<sup>2</sup>, the values of W/L of all transistors are calculated. Since, digital to analog converter is designed for 6-bit resolution; hence, minimum op-amp gain required is given by 2<sup>N+1</sup> i.e. 42dB and phase margin greater than 60<sup>0</sup> for system to be stable.

# 3.1 Design of Op-amp

The above requirements are satisfied by using design equations [7] given below:

Current through current mirror is obtained using,

Figure 5: Common Source Amplifier

Slew Rate =  $\frac{I_5}{C_c}$ .....(2) The dimensions of M<sub>1</sub>, M<sub>2</sub> is obtained using,

$$G_{BW} = \frac{g_{m1}}{C_c}$$

(3)

The dimensions of M<sub>3</sub>, M<sub>4</sub> is obtained using,

$$\left(\frac{W}{L}\right)_{3,4} = \frac{I_5}{\mu_P \times C_{OX} \times (V_{DD} - ICMR + + |VT3*(max)| + |VT1(MIN)|)^2}...(4)$$

The dimensions of  $M_5$ ,  $M_8$  is obtained using,

$$\left(\frac{W}{L}\right)_{5,8} = \frac{2 * I_5}{\mu_n * C_{OX} * (V_{DSAT5})^2}....(5)$$

The dimensions of M<sub>6</sub>, M<sub>7</sub> is obtained respectively using,

$$\left(\frac{W}{L}\right)_{6} = g_{m6} \left(\frac{W}{L}\right)_{4}$$

$$\frac{I_{7}}{I_{5}} = \frac{\left(\frac{W}{L}\right)_{7}}{\left(\frac{W}{L}\right)_{5}}$$

$$(7)$$

For system to be stable, phase margin to be greater than  $60^{\circ}$ .

Therefore miller capacitance is given by,

$$C_{C} > 0.22 * C_{L.....(8)}$$

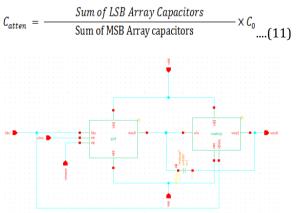

# 3.2 Design of Capacitor array

Unit capacitance [8] is calculated using,

$$\sqrt{\frac{kT}{C_{total}} + \frac{LSB^2}{12}} \leq \frac{LSB}{2}$$

$$C_{total} = \left[2^{\frac{N}{2}} + \left(2^{\frac{N}{2}} - 1\right)\right]C_0$$

(9)

Attenuation capacitance is calculated using,

Figure 7: Schematic of Two-Stage Op-amp

Figure (8) shows the schematic of 2:1 MUX as a switch passing  $V_{REF}$  or connecting output to GND when input is "LOGIC 1" and "LOGIC 0" respectively.

Figure 8: Schematic of 2:1 MUX as a Switch

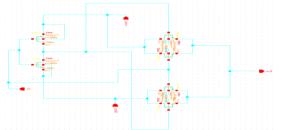

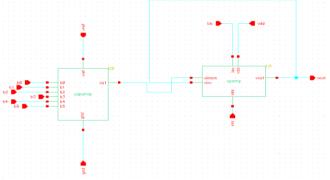

Figure (10) shows the schematic of the proposed DAC.

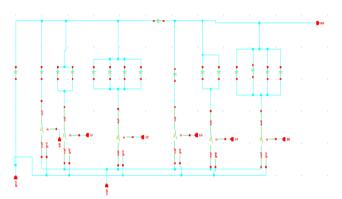

Figure 9: Schematic of capcitor array

Figure (10): Schematic of Proposed DAC

### **4.SIMULATION RESULTS**

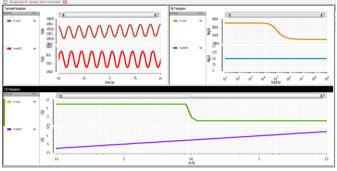

Figure (11) and (12) shows the simulation result of Opamp with gain of 52 dB and Phase Margin of  $86^{0}$ .

WWW.IRJET.NET

Figure 11: Simulation result of Two-Stage Opamp

Figure 12: Gain and Phase Plot of Two-Stage Opamp

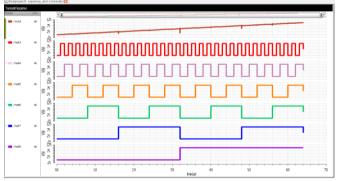

Figure (13) and (14) shows the simulation result and layout of Proposed DAC.

Figure 13: Simulation result of Proposed DAC

Figure 14: Layout of Proposed DAC

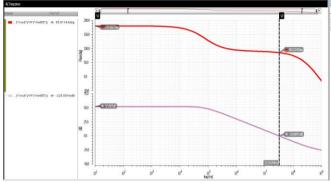

Chart-1 shows the DNL error of proposed DAC.

Chart-1: DNL of proposed DAC

### **5.Performance summary of proposed DAC**

|                   | [2]   | Proposed DAC |

|-------------------|-------|--------------|

| Technology        | 180nm | 180nm        |

| Supply voltage    | 1V    | 1V           |

| Resolution        | 6 Bit | 6 Bit        |

| Power dissipation | 1.5mW | 0.5mW        |

| UGW               | 16Mhz | 30Mhz        |

# **6.**CONCLUSION

In this paper, a DAC used in WSN transceivers has been investigated and designed. The design is mainly optimized for the low power, moderate resolution and moderate speed. Two stage op-amp is chosen as a basic component because of its advantages over other amplifiers. Two stage op-amp is simulated GPDK 180nm CMOS technology with gain and phase equal to 52dB and 86°. Power dissipation of 370µw is achieved. Split array based charge scaling DAC is simulated with GPDK 180nm CMOS technology. The DAC is designed for resolution of 6-bit wit DNL error less than 0.5LSB. Power dissipation achieved is  $499\mu$ W.

# **7.**FUTURE WORK

The power dissipation can be further reduced by using split array DAC with monotonic switching procedure. By using this method parasitic capacitance is balanced and matching of capacitance is enhanced.

### **8.R**EFERENCES

[1] Meghana Kulkarni, Muttappa Shingadi, G.H.Kulkarni, "6-Bit Charge Scaling DAC and SAR ADC", IJAREEIE, Vol.3, Issue 12, Dec 2014.

[2] Yuanliang Li, Zhiqun Li, "A Low-power 6-Bit D/A Converter Design for WSN Transceivers" IEEE 2011.

[3] Nirav A.Mehta, Bharat H.Nagpara, "Design and Implementation of 6-bit Charge Scaling Digital to Analog Convertor (DAC) using 45 Nano-meter Technology",IJSRD, Vol. 2, Issue 3, 2014.

[4] Behzad Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill International Edition.

[5] John M Yarbrough, "Digital Logic a`pplications and Design", Thomson Learning, 2001.

[6] Frank B. Boschke," Design of a 12bit 500Ms/s standalone charge redistribution Digital-to- Analog Converter" University of Twente, January 2008, pp.18-19.

[7] P.E.Allen and Holberg, CMOS Analog Circuit Design, Second Edition, Oxford University Press, 2002.

[8] Atul Thakur and Alpana Agarwal, "Low-Power Architectures and Self-Calibration Techniques of DAC for SAR-ADC implementation" International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering, Vol. 2, Issue 3, March 2014.

[9] Pouya Kamalinejad, Shahriar Mirabbasi, and Victor C.M. Leung "An Ultra-Low-Power SAR ADC with an Area-Efficient DAC Architecture"IEEE 2011.

[10] Hoonki Kim, YoungJae Min, Yonghwan Kim, and Soowon Kim," A Low Power Consumption 10-bit Rail-to-Rail SAR ADC Using a C-2C Capacitor Array" IEEE International Conference on Electron Devices and Solid-State Circuits, 2008.

[11] Abhisek Dey, T. K. Bhattacharyya," Energy-Efficient Dual Array Capacitive DAC and Switch Control for SAR ADC" IEEE International Conference on Computer Research and Development (ICCRD), 2011.

[12] Yi-Long Yu, Fu-Chen Huang and Chorng-Kuang Wang," A 1V 10-Bit 500KS/s Energy-Efficient SAR ADC Using Master-Slave DAC Technique in 180nm CMOS",IEEE International Symposium on VLSI Design, Automation and Test (VLSI-DAT), 2014 [13] Stefan Haenzsche, Rene Schüffny," Analysis of a Charge Redistribution SAR ADC with Partially Thermometer Coded DAC", IEEE European Conference on Circuit Theory and Design (ECCTD), 2013.

[14] Lin Cong," Pseudo C-2C Ladder-Based Data Converter Technique" IEEE Transactions on Circuits And Systems— II: Analog and Digital Signal Processing, Vol. 48, No. 10, October 2001

[15] Y. S. Yee, L. M. Terman, and L. G. Heller, "A two-stage weighted capacitor network for D/A–A/D conversion," *IEEE Journal of Solid-State Circuits*, vol. SC-14, pp. 778–781, August 1979.

[16] J. L. McCreary, "Matching properties, and voltage and temperature dependence of MOS capacitors," *IEEE Journal of Solid-State Circuits*, vol. SC-16, pp. 608–616, December 1981.

[17] Brian P. Ginsburg, "500-MS/s 5-bit ADC in 65-nm CMOS with Split Capacitor Array DAC", IEEE Journal Of Solid-State Circuits, Vol. 42, No. 4, April 2007.

[18] V. Liberali, S. Brigati, F. Francesconi, F. Maloberti, "Progress in High-speed and High-Resolution CMOS Data Converters" PROC. 20<sup>th</sup> International Conference on Microelectronics (miel'95), vol 1, nis, serbia, 12-1 4 September, *1995.*

[19] Anshul Agarwal, "Design of Low Power 8-Bit Digitalto-Analog Converter with Good Voltage- Stability", M.S. Thesis, International Institute of Information Technology, Hyderabad 2013.

[20] S.-W. Lee, H.-J. Chung and C.-H. Han, "C-2C digital-toanalogue converter on Insulator", Electronic Letters, vol 35, Issue 15, pp 1242-1243.

[21] Ashok Srivastava, Siva Yellampalli and Kalyan Golla, "Delta-IDDQ Testing of a CMOS 12-Bit Charge Scaling Digital-to-Analog Converter", 49th IEEE International Midwest Symposium on Circuits and Systems, 2006.