Volume: 02 Issue: 06 | Sep-2015 www.irjet.net p-ISSN: 2395-0072

# A MULTILEVEL INVERTER TOPOLOGY FOR RENEWABLE POWER GENERATION

Smt N. Sumathi <sup>1</sup>, R. Tulasi Ram<sup>2</sup>

<sup>1</sup> Assistant Professor, Department of EEE, JNTU Kakinada, Andhra Pradesh, India <sup>2</sup> Student, M.Tech(EEE) In Advanced Power Systems, JNTU Kakinada, Andhra Pradesh, India

\_\_\_\_\_\_\*\*\*\*\_\_\_\_\_

**Abstract -** — In this paper, a new multi-level inverter topology is developed and applied for injecting the real power of the renewable power into the grid to reduce the switching power loss, harmonic distortion caused by the switching operation of power electronic devices. Here this multi-level inverter configures with input dc capacitors, a dual-buck converter, a full-bridge inverter, and a filter. The input to the dual-buck converter is dc capacitor voltage sources. The power electronic switches of the full-bridge inverter are switched in low frequency synchronous with the utility voltage to convert the output voltage of the dual-buck converter to a multi-level ac voltage. The output current of the multi-level inverter is controlled to generate a sinusoidal current in phase with the utility voltage to inject into the grid. The five-level and nine-level inverter topologies are developed to verify the performance of the developed renewable power generation system and however the THD of both fivelevel and nine-level inverter topologies are analyzed. The simulation results show that the developed renewable power generation system reaches the expected performance

**Key Words:** Multilevel inverters, Total harmonic distortion, power electronics.

### 1. INTRODUCTION

The extensive use of fossil fuels has resulted in the global problem of greenhouse emissions. Moreover, as the supplies of fossil fuels are depleted in the future, they will become increasingly expensive. Thus, solar energy is becoming more important since it produces less pollution and the cost of fossil fuel energy is rising, while the cost of solar arrays is decreasing. In particular, small-capacity distributed power generation systems using solar energy may be widely used in residential applications in the near future. Generally the conventional single-phase inverter topologies interfacing to grid connection include half-bridge and full bridge[1],[3],[4]. All power electronic

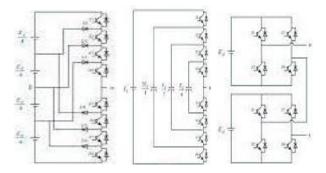

switches operate in high switching frequency in both halfbridge and full bridge inverters. The switching operation will result in switching loss. The loss of power electronic switch includes the switching loss and the conduction loss. The conduction loss depends on the handling power of power electronic switch. The switching loss is proportional to the switching frequency, voltage jump of each switching, and the current of the power electronic switches. The power efficiency can be advanced if the switching loss of the dc-ac inverter is reduced. The popular modulation strategies or the full-bridge inverter are unipolar modulation and bipolar modulation[4],[7]. Multilevel inverter can effectively reduce the voltage jump of each switching operation to reduce the switching loss and increase power efficiency. However, interest in the multilevel inverter has become more popular due to its advantages of better power efficiency, lower switching harmonics. The conventional single-phase multilevel inverter topologies further classified as the diodeclamped[2], the flying capacitor, and the cascade H-bridge types as shown in Fig. 1(a),(b),(c). Thus, both the performance and complexity should be considered in designing the multilevel inverter[8]-[9] .However, interest in the multilevel inverter has become more popular due to its advantages of better power efficiency, lower switching harmonics. In this paper, a five-level inverter and ninelevel inverter are developed and applied for injecting the real power of the renewable power into the grid. This developed multi-level inverter topologies are basically configured by an input dc capacitors, a dual-buck converter, a full-bridge inverter, and a filter. In this paper five-level inverter is developed that configures an two dc capacitors, a dual buck converter, a full-bridge inverter and a filter. In the below sections five level implementation is explained. The same implementation will be provided for nine level also, but in this actual circuit configuration, needs additional two capacitors and two switches in dual buck converter and finally both the

results of five and nine level inverter are as shown in the simulation results. Firstly the circuit configuration of five-level inverter which is applied to photovoltaic power generation system as shown.

**Fig 1**: Circuit configuration of conventional single phase five-level inverter.(a) Diode clamped. (b) Flying capacitor. (c) Cascade H-bridge.

### 2. CIRCUIT CONFIGURATION

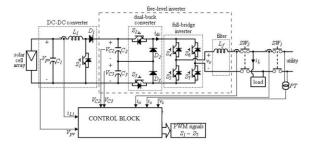

The actual circuit configuration of the five-level inverter that applied to renewable power generation system shown in fig2. As can be seen, it is configured by a solar cell array, a dc-dc converter, a five-level inverter, two switches, and controller. Here the Switches SW1 and SW2 are placed between between the five-level inverter and the utility, and these are used to disconnect the photovoltaic power generation system from the utility when islanding operation occurs. The load is placed between switches SW1 and SW2. The five-level inverter is being configured by two dc capacitors, a dual buck converter, a full-bridge inverter, and a filter. The dual-buck converter is configured by two buck converters. The two dc capacitors acts as energy buffers between the dc-dc converter and the five-level inverter. The output of the dual-buck converter is connected to the full-bridge inverter to convert the dc voltage to ac voltage. An inductor is placed at the output of the full bridge inverter to form as a filter inductor for filtering out the high-frequency switching harmonic generated by the dual-buck converter.

**Fig2**.A five-level circuit configuration of developed photovoltaic power generation

### 3. FIVE- LEVEL INVERTER OPERATION

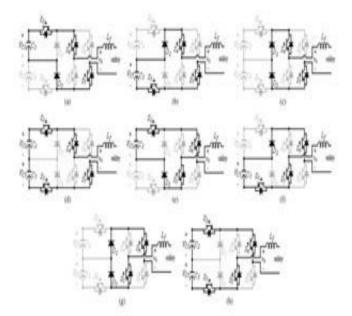

The five-level inverter operation can be classifed into eight modes. Modes 1–4 are for the positive half-cycle, and modes 5–8 are for the negative half-cycle as shown in fig3.

e-ISSN: 2395 -0056

Fig.3: Operation modes of the five-level inverter. (a) Mode 1. (b) Mode 2. (c) Mode 3. (d) Mode 4. (e) Mode 5. (f) Mode 6. (g) Mode 7. (h) Mode 8.

As seen in Fig. 3(a)-(d), the power electronic switches S4and S7 are in the ON state, and the power electronic switches S5 and S6 are in the OFF state during the positive half-cycle. On the contrary, the power electronic switches S4 and S7 are in the OFF state, and the power electronic switches S5 and S6 are in the ON state during the negative half-cycle. At mode 1, mode2, the output voltage of dual buck converter and five-level inverter are Vdc/2 and at mode3 output voltages of the dual buck converter and five-level inverter are 0, at mode4 output voltages of the dual-buck converter and five-level inverter are Vdc during positive half cycle. Modes 5–8 are the operation modes for the negative half cycle. The operations of the dual-buck converter under modes 5-8 are similar to that under modes 1-4, and the dual-buck converter can also generate three voltage levels Vdc/2, Vdc/2, 0, and Vdc, respectively.

# 3.1 VOLTAGE BALANCING OF FIVE-LEVEL INVERTER

Voltage balance of dc capacitors is very crucial in controlling the multilevel inverter. The voltage balance of dc capacitor voltages VC2 and VC3 can be controlled by the power electronic switches S2 and S3 easily. When the absolute of the utility voltage is smaller than Vdc/2, one power electronic switch either S2 or S3 is switched in high

Volume: 02 Issue: 06 | Sep-2015 www.irjet.net

frequency and the other is still in the OFF state. When the absolute of the utility voltage is higher than Vdc/2, one power electronic switch either S2 or S3 is switched in high frequency and the other is still in the ON state.

TABLE 1: ON/OFF STATE OF S2 AND S3.

|          |    | Vs < Vdc/2 | Vs >Vdc/2 |

|----------|----|------------|-----------|

| Vc2>Vc3  | S2 | PWM        | ON        |

|          | S3 | OFF        | PWM       |

| Vc2> Vc3 | S2 | OFF        | PWM       |

|          | S3 | PWM        | ON        |

### 4. CONTROL BLOCK DIAGRAM

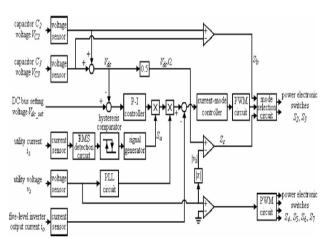

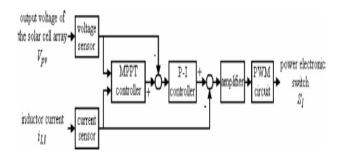

The developed photovoltaic power generation system consists of a dc-dc power converter and the five-level inverter Fig.4(a) shows the control block diagram of fivelevel inverter. In the operation of the five-level inverter, the dc bus voltage must be regulated to be larger than the peak voltage of the utility and the dc capacitor voltages of C2 and C3 must be controlled to be equal. Besides, the fivelevel inverter must generate a sinusoidal current in phase with the utility voltage to be injected into the utility. The control block diagram of dc-dc converter is shown in fig 4(b). The input of dc-dc converter is the output of solar cell array. The perturbation and observation method is adopted to obtain the function of MPPT, and it is incorporated into the controller of the dc- dc converter. The output of the MPPT controller is the desired output voltage of the solar cell array, and it is the reference voltage of the outer voltage control loop. The output voltage of the solar cell array is perturbed first, and then the output power variation of the solar cell array is observed to determine the next perturbation for the output voltage of the solar cell array. The output power of the solar cell array is calculated from the product of the output voltage of the solar cell array and the inductor current. Therefore, the output voltage of the solar cell array and the inductor current are detected and sent to a MPPT controller to determine the desired output voltage of the solar cell array. The detected output voltage and desired output voltage of the solar cell array are sent to a sub tractor, and the subtracted result is sent to a P-I controller. The output of the amplifier is sent to the PWM circuit. The output signal of the PWM circuit is the driving signal for the power electronic switch of the dc-dc converter.

e-ISSN: 2395 -0056

p-ISSN: 2395-0072

**fig4(a):** control block of five-level inverter

fig4(b): control block of dc-dc converter

**TABLE 2:**COMPARISION OF FIVE-LEVEL INVERTERS

|            | Cascaded | Flying    | Diode   | Developed |

|------------|----------|-----------|---------|-----------|

|            | H-bridge | capacitor | clamped | inverter  |

| Power      | 8        | 8         | 8       | 6         |

| electronic |          |           |         |           |

| switches   |          |           |         |           |

| capacitors | 2        | 4         | 2       | 2         |

| Voltage    | Hard     | Hard      | hard    | Easy      |

| palance of |          |           |         |           |

| capacitors |          |           |         |           |

| High       | 8        | 8         | 8       | 2         |

| requency   |          |           |         |           |

| switches   |          |           |         |           |

### 5- NINE -LEVEL INVERTER

Compare to Five level inverter nine level inverter have several advantages In order to reduce the THD we generally go for the nine level inverter. In the nine level

Volume: 02 Issue: 06 | Sep-2015 www.irjet.net p-ISSN: 2395-0072

inverter the output voltage have the nine levels for each cycle . The voltage jump in each switching operation of the nine level inverter is small compared to the five level inverter as a result the total harmonic distortion is less when compared to five level inverter . In the nine level inverter extra 2 switches and 2 capacitors are required. In this thesis five level inverter and nine level inverter topology for renewable power generation is done and the results are analysed for the both five level inverter and nine level inverter topology. The circuit configuration of the Nine-level inverter applied to a photovoltaic power generation system shown in fig6

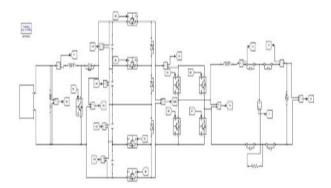

**fig5**: simulink model of circuit configuration of developed photo voltaic

### 5.1 CONTROLBLOCK

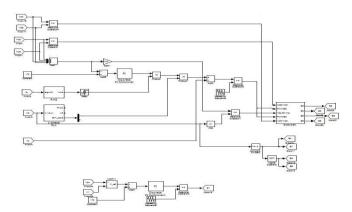

Fig.6 shows the control block diagram of nine-level inverter. In the operation of the nine-level inverter, the dc bus voltage must be regulated to be larger than the peak voltage of the utility and the dc capacitor voltages of C2 and C3 C4 C5 must be controlled to be equal. Besides, the nine-level inverter must generate a sinusoidal current in phase with the utility voltage to be injected into the utility. As seen in fig6, the voltages of dc capacitors C2, C3, C4 and C5 are detected and then added to obtain a dc bus voltage Vdc. The added result is subtracted from a dc bus setting voltage Vdc set. The dc bus setting voltage Vdc set is larger than the peak voltage of the utility. The subtracted result is sent to a P-I controller. the utility current is detected and sent to an RMS detection circuit. The output of the RMS detection circuit is sent to a hysteresis comparator that contains a low threshold value and a high threshold value. If the RMS value of the utility current is smaller than the low threshold value, the output of the hysteresis comparator is high, meaning the condition of islanding operation or power balance occurs. On the contrary, the output of the hysteresis comparator is low meaning the

utility is normal. The output of the hysteresis comparator is sent to a signal generator. The output signal of the signal generator is an islanding control signal Sa. The islanding control signal is a dc signal with unity amplitude if the output of the hysteresis comparator is low. On the contrary, the islanding control signal is a square wave with a frequency of 20 Hz (disturbance signal for islanding detection) when the output of the hysteresis comparator is high. The outputs of the PI controller and signal generator are sent to a multiplier, and the product of the multiplier is the amplitude of the reference signal. The utility voltage is detected and then sent to a phase-lock loop (PLL) circuit to generate an unity-amplitude sinusoidal signal whose phase is in phase with the utility voltage. The outputs of the multiplier and the PLL circuit are sent to the other multiplier. The product of this multiplier is the reference signal of the output current for the nine-level inverter. The output current of the nine-level inverter is detected by a current sensor. The reference signal and detected signal for the output current of the nine-level inverter are sent to a subtractor. The subtracted result is sent to a currentmode controller. The output of the current-mode controller is sent to a PWM circuit to generate a PWM signal. The detected dc capacitor voltages VC2, VC3 VC4 and VC5 are also sent to a comparator to obtain signal Sb. The output signal of the PWM circuit and signals Sb and Sc are sent to the mode selection circuit. The output of the mode selection circuit will generate the control signals of power electronic switches S2 S3 S4 S5 S8 and S9. The detected utility voltage is also sent to a comparator to complementary square signals synchronous with the detected utility voltage.. Therefore, the nine -level inverter can reduce the switching loss effectively.

e-ISSN: 2395 -0056

**fig 6**:control block diagram of nine-level inverter and control block of dc- dc converter

Volume: 02 Issue: 06 | Sep-2015 www.irjet.net p-ISSN: 2395-0072

**TABLE 3**:SIMULATION PARAMETERS

| Solar module           |         |  |  |  |

|------------------------|---------|--|--|--|

| Rate of                | 75W     |  |  |  |

| maximumpower           |         |  |  |  |

| Short current          | 5.0A    |  |  |  |

| Open Voltage           | 21.8V   |  |  |  |

| DC-DC converter        |         |  |  |  |

| Inductor Lf            | 2mH     |  |  |  |

| Capacitor Cf           | 470 μf  |  |  |  |

| Switch frequency       | 20KHz   |  |  |  |

| Nine-level inverter    |         |  |  |  |

| DC bus setting voltage | 170V    |  |  |  |

| Filter inductor Lf     | 1.4mH   |  |  |  |

| DC bus                 | 2200 μf |  |  |  |

| capacitor(C2,C3,C4,C5) |         |  |  |  |

| Switching              | 20KHz   |  |  |  |

| frequency(PWM)         |         |  |  |  |

| Utility voltage        | 110V    |  |  |  |

| Utility frequency      | 60Hz    |  |  |  |

### 6. SIMULATION RESULTS

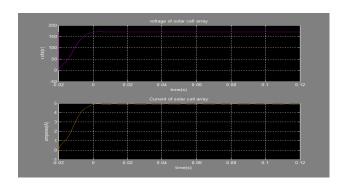

To check the performance of the photovoltaic power generation system using the five-level and nine level inverter, MATLAB/SIMULINK is used. The main parameters of the simulations are listed in Table II. The solar cell array consists of two strings, and each string contains eight solar modules connected in series. The capacity solar cell arrav 1.2 kW. The environmental temperature and radiation levels are 30.7° C and 922 W/m<sup>2</sup> respectively .The temperature of solar module 52.3°C The maximum power output of solar cell array is maintained about 830W. fig7:voltage and current characteristics of the solar cell array is shown below

fig7:voltage and current characteristics of the solar cell array

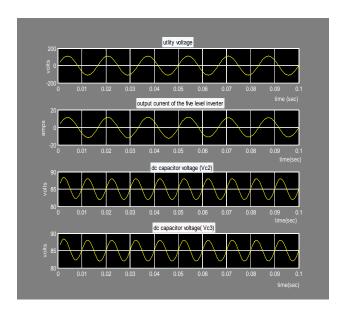

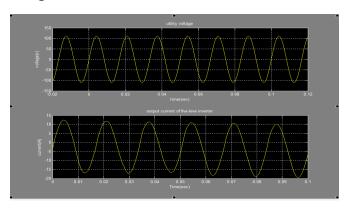

fig8:simulation results of five-level inverter.(a) Utility voltage (b) output current of five-level inverter (c) dc capacitor voltage(Vc2). (d) dc capacitor voltageVc3)

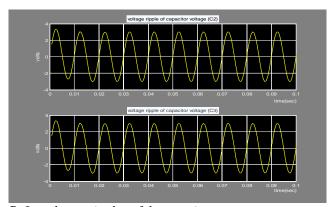

fig9: voltage ripples of dc capacitors

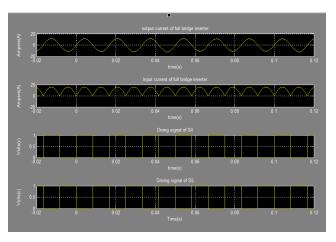

Fig 10. Simulation results for full-bridge inverter of the five-level inverter. (a) Output current of the full-bridge inverter io. (b) Input current of the full bridge inverter idc. (c) Driver signal of S4. (d) Driver signal of S5

Volume: 02 Issue: 06 | Sep-2015 www.irjet.net p-ISSN: 2395-0072

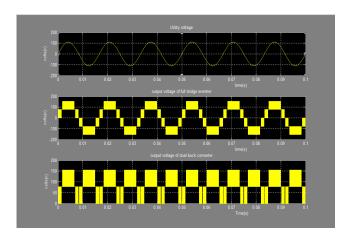

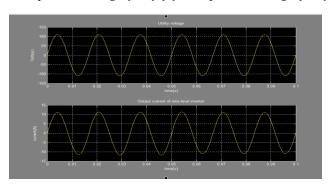

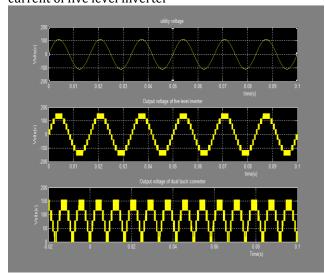

**fig11**:simulation results of five-level inverter (a) Utility voltage (b) output voltage of five -level inverter (c) output voltage of dual buck converter

**fig12:** Simulation results under distorted utility voltage (a) Utility voltage (b) output current of five-level inverter

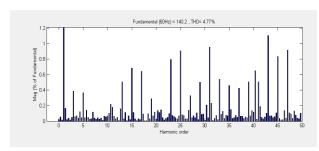

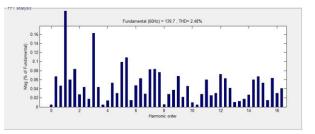

**fig13**: harmonic distortions of (a)utility voltage (b) output current of five-level inverter

The output power of the solar cell array in the developed photovoltaic power generation system is about 830 W. Therefore, the developed photovoltaic power generation system can track the maximum power point of the solar cell array effectively As seen in Fig. 8(b), the output current of the five-level inverter is sinusoidal and in phase with the utility voltage. The total harmonic distortion (THD%) of the utility voltage and the output current of the five-level inverter are 4.77% and 2.48%, respectively. As seen in Fig.8(c) and (d), both dc capacitor voltages VC2 and VC3 remain in balance, and their voltage is about 85 V, respectively. Therefore, the dc bus voltage is regulated at 170 V. This verifies the fivelevel inverter can perform the functions of converting solar power to ac power with unity power factor, low and balancing two dc capacitor voltages effectively Fig.9(a) and (b) show the peak-to-peak value of the voltage ripple at dc capacitors C2 and C3 is about 7 V. As seen in. Fig.10 shows the simulation results for the fullbridge inverter of the five-level inverter. As can be seen, the input current ide of the full-bridge inverter shown in Fig.10(b) is the absolute of the output current of the full bridge inverter shown in Fig. 10(a). As seen in Fig. 10(c) and (d), the switch frequency of the power electronic switches S4 and S5 is 60 Hz. This verifies the power electronic switches of the full-bridge inverter are switched in low frequency, and the full-bridge inverter can convert the dc power into ac power by commutating. The above figures shows the simulation voltage of the five-level inverter .As seen in Fig.11(c),the dual-buck converter output a dc voltage with three levels Vdc, Vdc/2, and 0.Fig.11(b) shows the output voltage of the dual-buck converter is further converted to an ac voltage with five voltage levels Vdc, Vdc/2, 0, -Vdc/v2, and -Vdc by the full-bridge inverter. The voltage variation of each level is Vdc/2.this verified that the five-level inverter can generate a five-level output ac voltage according to the utility voltage and only the power electronic switches of the dual-buck converter is switched in high frequency. Fig.12 shows the simulation results for the developed photovoltaic power generation .system under the distorted utility voltage. As seen in Fig. 12(a), the utility voltage is distorted. As seen in Fig. 12(b), the output current of the five-level inverter is still close to sinusoidal, and its THD% is only 5.6% and the power factor is 0.99. The total harmonic distortion (THD%) of the utility voltage and the output current of the five-level inverter are 4.73% and 2.48%, respectively which are shown in fig 13.

e-ISSN: 2395 -0056

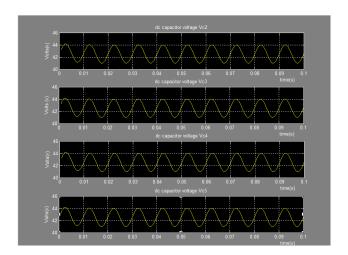

**fig14**:simulation results of nine-level inverter (a) dc capacitor voltage(Vc2). (b) dc capacitor voltage(Vc3) (c) dc capacitor voltage (Vc3) (d) dc capacitor voltage (Vc5)

**fig15**: simulation results of utility voltage and output current of five level inverter

$\mbox{fig16}$  :simulation results of nine-level inverter (a) Utility voltage (b) output voltage of nine -level inverter (c) output voltage of dual buck converter

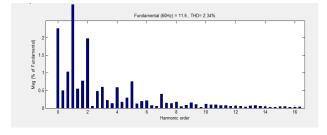

As seen in fig14.(a),(b),(c),(d) both the capacitor votages remain in balance and their voltage is about 42.5v.The above figures shows the simulation voltage of the nine-level inverter .As seen in Fig.16(c),the dual-buck converter output a dc voltage with five levels each level voltage variation of Vdc , 3Vdc/4, Vdc/2, Vdc/4 and 0 .Fig.16(b) shows the output voltage of the dual-buck converter is further converted to an ac voltage with nine voltage levels by the full-bridge inverter. Above fig15 shows the simulation results of the nine level inverter . The utility voltage and output current of nine level inverter is in phase.

e-ISSN: 2395 -0056

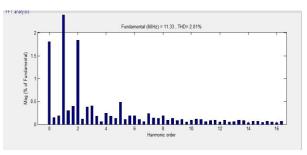

**fig 4.15:**harmonic distortions of utility voltage and output current of five-level inverter

The voltage and the output current of the five-level inverter are 2.48% and 2.01%, respectively .

**TABLE 4**:COMPARISION OF FIVE-LEVEL AND NINE LEVEL TOPOLOGIES

|                                | Developed<br>Topology<br>(five-level inverter) | Developed<br>Topology (nine-<br>level inverter) |

|--------------------------------|------------------------------------------------|-------------------------------------------------|

| Power electronic switches      | 6                                              | 8                                               |

| Capacitors                     | 2                                              | 4                                               |

| Voltage<br>balance             | Easy                                           | Easy                                            |

| High-<br>frequency<br>switches | 2                                              | 4                                               |

| Voltage<br>THD                 | 4.73 %                                         | 2.48 %                                          |

| Current<br>THD                 | 2.53 %                                         | 2.01 %                                          |

Volume: 02 Issue: 06 | Sep-2015 www.irjet.net p-ISSN: 2395-0072

### 7. CONCLUSION

A photovoltaic power generation system with a five-level inverter and nine level inverter is developed in this thesis. The five level and nine level inverter topology can perform the functions of regulating the dc bus voltage, converting solar power to ac power with sinusoidal current and in phase with the utility voltage, balancing the two dc capacitor voltages. The Simulation results verify the developed photovoltaic power generation system, and the five-level and nine level inverter achieves the expected performance .The total harmonic distortion of both topology are analysed and compare the performance of both nine level and five level inverter topology

### REFERENCES

- [1] D. Puyal, L. A. Barragan, J. Acero, J. M. Burdio, and I. Millan, "An FPGA-based digital modulator for full- or half-bridge inverter control," *IEEE Trans. Power Electron.*, vol. 21, no. 5, pp. 1479–1483, Sep. 2006.

- [2] O. Lopez, F. D. Freijedo, A. G. Yepes, P. Fernandez-Comesaa, J. Malvar, R. Teodorescu, and J. Doval- Gandoy, "Eliminating ground current in a transformer less photovoltaic application," *IEEE Trans. Energy Convers.*, vol. 25, no. 1, pp. 140–147, Mar. 2010.

- [3] B. R. Lin and C. L. Huang, "Implementation of a Shuntseries compensator for nonlinear and voltage sensitive load," in *Proc. IEEE Power Electron. Motion Control Conf.*, 2006, pp. 1–5.

- [4] U. S. Selamogullari, D. A. Torrey, and S. Salon, "A systems approach for a stand-alone residential fuel cell power inverter design," *IEEE Trans. Energy Convers.*, vol. 25, no. 3, pp. 741–749, Sep. 2010.

- [5] J.Gafford,M. Mazzola, J. Robbins, and G. Molen, "Amulti-kilowatt high frequency ac-link inverter for conversion of low-voltage dc to utility power voltages," in *Proc. IEEE Power Electron. Spec. Conf.*, 2008, pp. 3707–3712.

- [6] T. H. Ai, J. F. Chen, and T. J. Liang, "A random switching method for HPWM full-bridge inverter," *IEEE Trans. Ind. Electron.*, vol. 49, no. 3, pp. 595–597, Jun. 2002.

- [7] C. Y. Chen, Y. H. Lin, J. F. Chen, and R. L. Lin, "Design and implementation of DSP-based voltage frequency conversion system," in *Proc. Int. Symp. Comput. Commun. Control Autom.*, May 2010, pp. 435–438.

- [8] M. Chithra and S. G. B. Dasan, "Analysis of cascaded H bridge multilevel inverters with photovoltaic arrays," in *Proc. Int. Conf. Emerging Trends Elect. Comput. Technol.*, Mar. 2011, pp. 442–447.

- [9] N. Yousefpoor, S. H. Fathi, N. Farokhnia, and S. H. Sadeghi, "Application of OHSW technique in cascaded multi-level inverter with adjustable dc sources," in *Proc. Int. Conf. Electric Power Energy Convers. Syst.*, 2009,pp.1-6.

- [10] S. De, D. Banerjee, K. Siva Kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," *IET Power Electron.*, vol. 4, no. 4, pp. 384–392, Apr. 2011.

- [11] A. Nami, F. Zare, G. Ledwich, A. Ghosh, and F. Blaabjerg, "Comparison between symmetrical and asymmetrical single phase multilevel inverter with diodeclamped topology," in *Proc. IEEE Power Electron. Spec. Conf.*, Jun. 2008, pp. 2921–2926.

- [12] E. Ozdemir, S. Ozdemir, and L. M. Tolbert, "Fundamental-frequency modulated six-level diodeclamped multilevel inverter for three-phase stand-alone photovoltaic system," *IEEE*