Volume: 03 Issue: 04 | Apr-2016

# **Design and Comparative Analysis of Single Gate Tunnel FET and MOSFET**

S. M. Turkane<sup>1</sup>, V. B. Shinde<sup>2</sup>, A. A. Shingade<sup>2</sup>, S. K. Taralkar<sup>2</sup>

<sup>1</sup>Professor, Department of Electronics and Telecommunication, Pravara Rural Engineering College, Loni, India. <sup>2</sup>Student, Department of Electronics and Telecommunication, Pravara Rural Engineering College, Loni, India.

\*\*\*\_\_\_\_\_

**Abstract** - The Tunnel Field effect transistor (Tunnel-FET) may be a new style of transistor. Although its structure is extremely kind of like a metal-oxide-semiconductor fieldeffect transistor (MOSFET), the basic shift mechanism differs. We know that MOSFET has many limitations so new technology is developed as Tunnel Field Effect Transistor (TFET). The tunneling field effect transistor uses the quantum-mechanical generation of carriers by band-toband tunneling. It doesn't show the short channel effects just like the MOSFETs all the way down to a gate length within the vary of a multiple of the electron wave-length. This work elaborates comparison of different characteristics of MOSFET and TFET.In this paper we have designed and simulated a homo-junction n-Tunnel FET. We use Si, Ge, SiGe (with concentration Si=65%(0.65), Ge=35%(0.35)) as body and vary the gate material for getting better results. The simulation is done on licenced Cogenda TCAD software (Version 1.7.4). We have analysed transfer characteristics, output characteristics, C-V characteristics of all these devices. We compare ON current  $(I_{ON})$ , OFF current  $(I_{OFF})$ , Sub-threshold slope, Time delay, Transconductance, and PDP of these devices. ForSi-TFET, we got SS of 57.56 mV/dec, OFF-state current of 0.255896 pA/µm, ON-state current of 46.8133  $\mu A/\mu m$ . The Tunnel-FET is very promising candidate for low power high speed application but their low ON current must be improved to be compatible with future VLSI circuits.

Key Words: MOSFET, TFET, band to band tunnelling, Power Delay Product (PDP), Visual TCAD.

# **1.INTRODUCTION**

MOSFET is basic building block of most integrated circuits because the MOSFET has become tinier, generation by generation, the chips supported it became a lot of quicker and fewer power hungry than their predecessors [13]. With the scaling of MOSFET, power supply should also be scaled down to reduce the power density. However, even within the ideal case of infinite gate capacitance, the SS of MOSFETs can't be reduced below 60mV/decade at room temperature. Other limitations of MOSFET are Channel Length Modulation, Short Channel Effects (SCEs), Velocity Saturation of Carriers, Impact Ionization, Narrow Channel

Effect, Subthreshold Conduction [3]. The Tunnel Field Effect Transistor (TFET) measures asone of the foremost promising successors of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) owing to their potential for sub-60mV/decade subthreshold swing. Such a reduced swing could be a necessary demand for ultra-low power, ultra-low voltage and high speed operation of next generation VLSI circuits. The gate controlled band to band tunneling is the working rule of the semiconductor unit and its basic structure could be a gated P-I-N diode. Compared to MOSFET, TFET has many merit of list; appropriate for low power applications, owing to lower leak current, higher immunity to short channel effects, subthreshold swing not restricted to 60mV/decade [19].

In this work, different TFETs with designs and characteristics are studied. This paper is organised as follows. Section II introduces working principle of TFET. In section III we have discussed our proposed methodology. Section IV represents simulation and results. Section V presents the conclusion.

## **2. PRINCIPLES OF TFET**

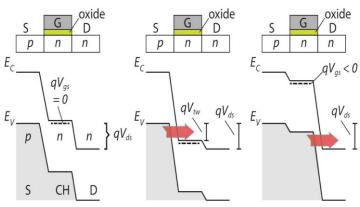

Tunnel FETs utilize a MOS gate to manage the band-toband tunneling across a degenerate tangency. The device is mostly OFF once zero bias is applied to the gate, the Conduction band minimum of the channel is above the valence band most of the supply, and therefore band-toband tunneling is suppressed [20]. A tunneling window disclose as a result of the conduction band of the channel is shifted below the valence band of the supply. Electrons inside the valence band with energy throughout this tunneling window tunnel into empty states inside the channel and conjointly the transistor is ON [10].

International Research Journal of Engineering and Technology (IRJET) e-I

IRJET Volume: 03 Issue: 04 | Apr-2016

www.irjet.net

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

**Fig -1**: Schematic cross-section and energy band diagram of an n-channel TFET when the device is biased in (a) OFF (b) ON and (c) ambipolar state [10].

# **3. METHODOLOGY**

We have done simulation in license Cogenda Visual TCAD software. We are designing and simulating MOSFET and TFET. We have used different body materials and compared with each other and to evaluate best performance among them. Tunnel FET required Band to Band tunneling model. We have used Kanes Band to Band tunneling model with A.BTBT=  $3.9E+22 \text{ eV}^{-(1//2)} \text{ cm}^{-1} \text{ s}^{-1}\text{V}^{-2}$  and B.BTBT=  $2.25E+07 \text{ V} \text{ cm}^{-1}\text{ eV}^{-(2/3)}$  these parameters. We also used Lombardi mobility model. We have plotted I<sub>D</sub>-V<sub>G</sub> and C-V Characteristics of Si-TFET, Ge-TFET, SiGe-TFET to calculate various parameters like SS, PDP, Time delay, Transconductance, PDP, Time Delay, SS can be calculated using following formulas

| $PDP = C_G \times V_{DD}^2$                 | (1) |     |

|---------------------------------------------|-----|-----|

| Time Delay(T) = $\frac{cg \times Vdd}{lon}$ | (2) |     |

| $SS = \frac{Vdd}{\log \frac{Ion}{Ioff}}$    |     | (3) |

#### 4. SIMULATION AND RESULTS

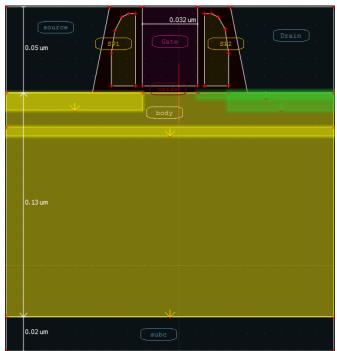

Below Fig. 2 shows the final device structure of TFET we have designed in the Visual TCAD for simulation. The parameter value used in design is as described in Table 1.

Fig -2: Device structure of TFET in TCAD

**Table -1:** Parameter & Values of TFET Used in TCADSimulation.

| Sr.<br>No. | Parameter            | Length | Material<br>Used                      | Doping /<br>Mesh Size                         |  |

|------------|----------------------|--------|---------------------------------------|-----------------------------------------------|--|

| 1          | Gate                 | 32nm   | nPolySi                               | Mesh size=<br>0.003µm                         |  |

| 2          | Source               | 50nm   | Al                                    | 1e+20<br>(Y=0.002)<br>(Acceptor)              |  |

| 3          | Drain 50             | 50mm   | Al                                    | 1e+19<br>(Y=0.003)                            |  |

|            |                      | 50nm   | Lower<br>Drain<br>Doping              | 1e+18<br>(Donor)                              |  |

| 4          | Body                 | 130nm  | Si <sub>0.65</sub> Ge <sub>0.35</sub> | Mesh size=<br>0.005 µm<br>1e+17<br>(Acceptor) |  |

| 5          | Oxide                | 4nm    | SiO <sub>2</sub>                      | Mesh size=<br>0.004µm                         |  |

| 6          | Substrate            | 20nm   | Al                                    | Mesh size=<br>0.004µm                         |  |

| 7          | Spacer1 &<br>Spacer2 | 18nm   | Nitride                               | Mesh size=<br>0.004µm                         |  |

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

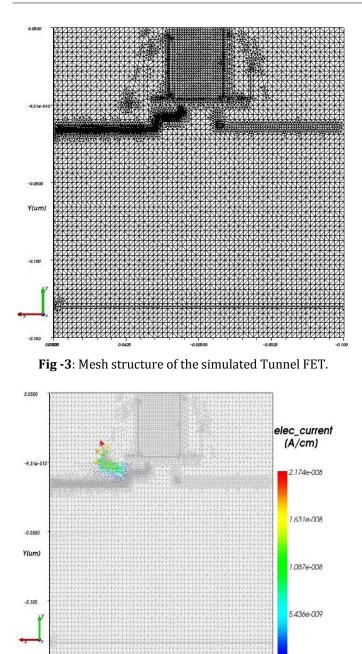

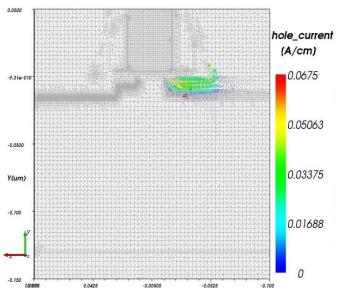

**Fig -4**: Flow of electron current in TFET at Vds = 1.2V.

-0.052

0.042

-0.150

Fig -5: Flow of hole current in TFET at Vds = 1.2V

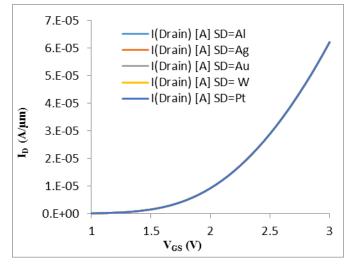

Fig -6:  $I_DV_G$  Characteristics for Al-Gate and Varying Source & Drain material

0

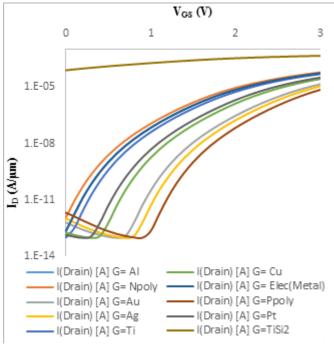

Fig -7:  $I_DV_G$  Characteristics for Source & Drain of Al and Varying Gate material

Material properties have various effects on device characteristics. Drain, Source and gate metal contact material should be a good conductor. Gate material has very significant effect on drain current which control the conduction channel, so we varied gate material keeping Drain & Source as Aluminium as varying Drain and Source doesn't affect the characteristics as shown in fig 6.

As shown in Fig.7 we use various gate material as Al, N-poly, Au, Ag, Ti, Cu, Elec, P-poly, Pt, TiSi<sub>2</sub> out of which N-poly gives better results among other materials.

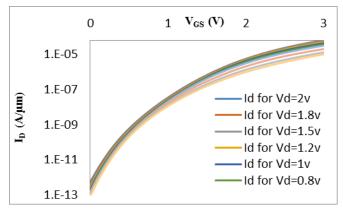

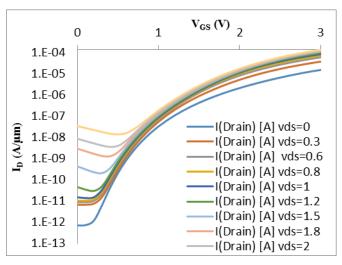

Fig -8:  $I_DV_G$  Characteristics of Si-TFET for various Vds in  ${\rm Log}_{10}$  Scale.

Id-Vg characteristics for 0V <Vds< 2V of the 32 nm Npoly gate and Si-TFET is plotted on logarithmic scale. For Si TFET for Vds=1.2V,  $I_{off} = 2.55896e-13$  (A/µm) at Vgs=0Vand  $I_{on}$ =4.68133e-05 (A/µm) at Vgs=3V.

Fig -9:  $I_DV_G$  Characteristics of Ge-TFET for various Vds in  $\text{Log}_{10}$  Scale.

Id-Vg characteristics for 0V <Vds< 2V of the 32 nm Npoly gate and Ge-TFET is plotted on log scale. For higher gate voltage current gets saturated due to saturation of tunneling channel. For Ge-TFET for  $V_{ds}$ =1.2V  $I_{off}$  = 4.52214e-11(A/µm) at Vgs=0V and  $I_{on}$ =9.73722e-05(A/µm) at Vgs=3V.

**Fig -10**:  $I_DV_G$  Characteristics of  $Si_{0.65}Ge_{0.35}$ -TFET for various Vds in Log<sub>10</sub> Scale.

Id-Vg characteristics for 0V <Vds< 3V of the 32 nm Npoly gate and  $Si_{0.65}Ge_{0.35}$ -TFET is plotted on logarithmic scale. For SiGe TFET for  $V_{ds}$ =1.2V,  $I_{off}$  = 1.48351e-12 (A/µm) at Vgs=0Vand  $I_{on}$ =6.99737e-05 (A/µm) at Vgs=3V.

International Research Journal of Engineering and Technology (IRJET)e-ISSN: 2395 -0056Volume: 03 Issue: 04 | Apr-2016www.irjet.netp-ISSN: 2395-0072

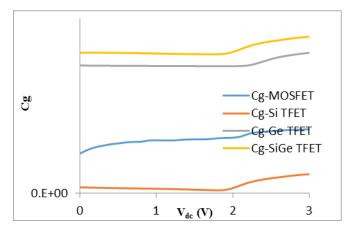

Fig -11: C-V Characteristics of MOSFET & TFET

Above Fig. 11 shows the C-V characteristics of MOSFET and TFET for different body material. The limiting issue for attaining high cut-off frequency is that the low price of trans-conductance and a high gate-to drain capacitance ( $C_{gd}$ ). The dynamic behaviour of a device is that the results of device capacitive effects caused by the charges hold on within the device [21]. Simulated graph shows that Si-TFET has lowest capacitance whereas Si<sub>0.65</sub>Ge<sub>0.35</sub> -TFET has very high capacitance.

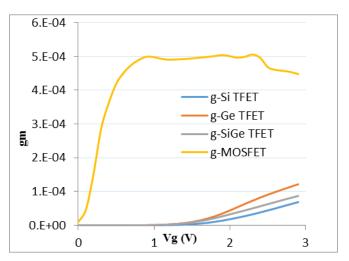

Fig -12: Transconductance of MOSFET & TFET.

Above Fig. 12 shows the Transconductance of MOSFET and TFET. Transconductance of MOSFET is very high as compare to the TFET. Above graph shows the transconductance (gm) for TFET of different material. As we have used Si, Ge and  $Si_{0.65}Ge_{0.35}$  materials for body we have calculated Transconductance curve for these TFETS. We have compared these graphs and from these graph we can observe that transconductance of silicon TFET is lower than Ge TFET and  $Si_{0.65}Ge_{0.35}$ - TFET has values that is between these two.Comparative analysis results of MOSFET and TFET are as shown in Table 2.

**Table -2:** Comparison of Different Parameter of MOSFET and TFET  $V_{DD}$ =0.3V AND  $V_{DD}$ =1.2V.

| Sr.<br>No. | Device                                        | I <sub>on</sub> Λ<br>(A/μm) | I <sub>off</sub><br>(A/μm) ψ | Subthreshold<br>Swing (SS)<br>(mV/dec) |                | Transcon<br>ductance<br>(gm)<br>(S) ↑ | <b>PDP</b><br>(J/μm) <b>γ</b> | Time<br>Delay<br>(s) |

|------------|-----------------------------------------------|-----------------------------|------------------------------|----------------------------------------|----------------|---------------------------------------|-------------------------------|----------------------|

|            |                                               |                             |                              | $V_{dd}$ =0.3 V                        | $V_{dd}$ =1.2V |                                       |                               |                      |

| 1          | MOSFET                                        | 128.714e-05                 | 336348e-12                   | 175.57                                 | 230            | 4907e-7                               | 3.922e-16                     | 2.53894e<br>-13      |

| 2          | Si TFET                                       | 4.68133e-05                 | 0.255896e-<br>12             | 50.41                                  | 214            | 7.97e-07                              | 3.183e-17                     | 5.666235<br>e-13     |

| 3          | Ge TFET                                       | 9.73722e-05                 | 45.2214e-12                  | 71.76                                  | 329            | 27.52e-07                             | 9.449e-16                     | 80.86858<br>e-12     |

| 4          | Si <sub>0.65</sub> Ge <sub>0.35</sub><br>TFET | 6.99737e-05                 | 1.48351e-12                  | 57.56                                  | 227            | 25.74e-07                             | 1.036e-15                     | 123.3240<br>e-13     |

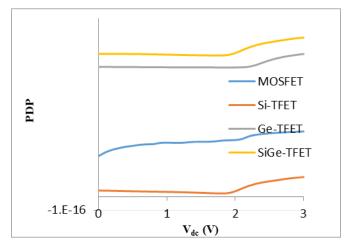

Fig -13: PDP of MOSFET & TFET.

Power Delay Product gives us how much power is consumed by the device at that particular delay. Combining these two parameters is important as these are the main performance parameters of the device.

# **5. FUTURE SCOPE AND CONLUSION**

This work has been analysed thoroughly about the subthreshold swing performances of advanced Tunnel FET devices of 32nm gate length with the MOSFET. The TFET has lower OFF-current than the traditional MOSFET, each TFET type that is simulated have comparatively similar low ON-current thus increasing the ON-current may be a huge challenge ahead. For the TFET there is still a need to both further decrease SS and increase  $I_{ON}$  to be a competitive replacement for the conventional MOSFET. By increasing the source doping it becomes possible to increase the overall tunnel current.

To satisfy the requirement of  $I_{ON}$  current according to ITRS low band gap material for source high doping concentration required. Also further Hetro-structure can be used to get steep subthreshold slope and high  $I_{ON}$ . Ambipolar behaviour of TFET can be reduced using thick buried oxide layer.

## **6. CONCLUSIONS**

In this work, performance of TFET is analysed and studied. We have proposed and mentioned the fundamental static operation, and simulated the characteristics of tunnel FET. TFET has lower subthreshold slope than MOSFET. Tunnel FET is applicable for low power devices as it gives lower off current. It is difficult to achieve high  $I_{ON}$  degrading  $I_{OFF}$ , and subthreshold slop below 60mV/dec. Main disadvantage of Si-TFET is that the ON current is very low so we don't satisfy the ITRS ON current value. Which is not compatible with current CMOS based circuits. So we changed Si body with Ge and Si<sub>0.65</sub>Ge<sub>0.35</sub> compound material which are low band gap material, which reduces tunneling distance at source channel junction. But improvement in ON current is not observed. In-spite of these drawback of TFET, it is promising candidate for future low power applications. Therefore main focus for TFET device is to improve the ON current so thatit can fully replace the conventional MOSFET technology in future VLSI circuits.

# REFERENCES

- [1] Adrian M. Ionescu and Heike Riel, "Tunnel field effect transistors as energy efficient electronic switches," Nature, Vol. 479, Nov. 2011, pp. 329-337.

- [2] Gholizadeh M., Hosseini S. E., "An analytical model for transfer characteristics and sub- threshold swings in double-gate tunnel FETs,"2014 22nd Iranian Conference on Electrical Engineering (ICEE), Tehran, May 2014, pp.48-52.

- [3] Satish M Turkane, A. K. Kureshi, "Review of Tunnel Field Effect Transistor (TFET)," International Journal of Applied Engineering Research, Vol. 11, No. 7, 2016, pp 4922-4929.

- [4] Lei Yao, Renrong Liang, Chunsheng Jiang, Jing Wang and Jun Xu, "Investigation of the Junction less Line Tunnel Field-Effect Transistor," 2014 International Symposium on Next-Generation Electronics (ISNE), Kwei-Shan, May 2014, pp. 1-2.

- [5] Rahim Esfandyarpour, "Tunneling Field Effect Transistors," coursework of PH250, Stanford University, Spring 2012.

- [6] HAO LU & ALAN SEABAUGH, "Tunnel field effect transistor: state of the Art," IEEE Electron Devices Society, Vol. 2, No. 4, July 2014, pp. 44 – 49.

- [7] Akhila Kamal & B. Bindu, "Design of Tunnel FET based low power digital circuits," 18th International Symposium on VLSI Design and Test, , Coimbatore, July 2014.

- [8] David Esseni, Manuel Guglielmini, Bernard Kapidani, Tommaso Rollo, and Massimo Alioto, "Tunnel FETs for Ultralow Voltage Digital VLSI Circuits: PartI—Device-Circuit Interaction and Evaluation at Device Level," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 12, Feb. 2014, pp. 2488 -2498.

- [9] Massimo Alioto and David Esseni, "Tunnel FETs for Ultra-Low Voltage Digital VLSI Circuits: Part II– Evaluation at Circuit Level and Design Perspectives," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 12, March 2014, pp. 2499 – 2512.

- [10] Hao Lu, Trond Ytterdal, and Alan Seabaugh, "Universal TFET model implementation in Verilog-A,"University of Notre Dame, Norwegian University of Science and Technology, January 2015.

- [11] Matthias Schmidt, "Fabrication, Characterization and Simulation of Band-to-Band Tunneling Field-Effect Transistors Based on Silicon-Germanium," October 2013.

- [12] Peng-Fei Wang, "Complementary Tunneling-FETs (CTFET) in CMOS Technology," December 2003.

- [13] A. C. Seabaugh and Q. Zhang, "Low-voltage Tunnel transistors for beyond CMOS logic," Proc. IEEE, Vol. 98, No. 12, Dec. 2010, pp. 2095–2110.

- [14] Woo Young Choi, Byung-Gook park, Jong Duk Lee, "Tunneling field effect transistor (TFET) with subthreshold swing (SS) less than 60mV/dec," IEEE Electron Device Letters, Vol. 28, No. 8, Aug. 2007, pp. 743-745.

- [15] Ram Asra, Mayank Shrivastava, V. R. M. Murali, Rajan k. Pandey, Harald Gossner and V. Ramgopal Rao, "A Tunnel FET for Vdd scaling below 0.6V with a CMOS Comparable performance," IEEE Transaction on Electron Devices, Vol. 58, No.7, July 2011, pp. 1855-1863.

- [16] Ravindhiran Mukundrajan, Matthew Cotter, Vinay Saripalli, Marry Jane Irwin, Suman Datta & Vijaykrishnan Narayanan, "Ultra Low power circuit design using Tunnel FETs," IEEE Computer Society Annual Symposium on VLSI, Amherst, MA, 2012.

- [17] L. Megala, B. Devanathan, R. Venkatraman, A. Vishnu kumar, "Tunneling Field Effect Transistors for Low Power Digital Systems," International Journal of Innovative Technology & Exploring Engineering, Vol. 2, No. 5, April 2013.

- [18] Woo Young Choi, "Comparative study of tunneling Field effect transistors and Metal Oxide Semiconductor Field Effect Transistors," Japanese Journal of applied physics, Vol. 49, No. 4, 2010.

- [19] Aswathy M, Nitha M Biju, Rama Komaragiri, "Comparison of a 30nm Tunnel Field Effect Transistor and CMOS Inverter Characteristics," Department of ECE, Third International Conference on Advances in Computing and Communications, Cochin, 2013.

- [20] C.H. Pavan kumar, Dr. K. Sivani, "Analyzing the impact of TFETs for ultra-low power design applications," International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT).

- [21] Narang Rakhi, Manoj Saxena, R. S. Gupta, and Mridula Gupta, "Device and Circuit Level Performance Comparison of Tunnel FET Architectures and Impact of Heterogeneous Gate Dielectric," Journal of

Semiconductor Technology and Science, Vol.13, No.3, June, 2013, pp. 224-236.

[22] Visual TCAD user's guide by COGENDA, http://www.cogenda.com

#### **BIOGRAPHIES**

Satish M Turkane is Pursuing his Ph. D and working as Associate Professor in E&Tc Engineering at Pravara Rural Engineering College Ahmednagar, Loni. Maharashtra, India.He is a Life Member of ISTE, IEI and IETE.

Vinit B Shinde is pursuing his B.E in Pravara Rural Engineering Ahmednagar, college. Loni, Maharashtra, India under Savitribai Phule Pune University, Pune

Ashok A Shingade is pursuing his B.E in Pravara Rural Engineering college, Loni, Ahmednagar, Maharashtra, India under Savitribai Phule Pune University, Pune.

Sanket K Taralkar is pursuing his B.E in Pravara Rural Engineering college. Loni, Ahmednagar, Maharashtra, India under Savitribai Phule Pune University, Pune.