e-ISSN: 2395 -0056

p-ISSN: 2395-0072

## A CIRCUIT TO INCREASE HIGH THROUGHPUT OF DM

#### BANOTH REVATHIC, 1 H.RAMESH BABU<sup>2</sup>

<sup>1</sup> m.tech student,ece department, svs group of institutions, warangal, telangana. <sup>2</sup> associate professor, ece department, sys group of institutions, warangal, telangana.

**Abstract** - Within this paper, we advise a maturing-aware multiplier design having a novel adaptive hold logic (AHL) circuit. Meanwhile, the negative bias temperature instability effect happens whenever a pMOS transistor is under negative bias, growing the brink current from the pMOS transistor, and reducing multiplier speed. An identical phenomenon, positive bias temperature instability, happens when an nMOS transistor is under positive bias. Digital multipliers are some of the most important arithmetic functional models. The general performance of those systems is dependent around the throughput from the multiplier. Both effects degrade transistor speed, as well as in the lengthy term, the machine may fail because of timing violations. Therefore, you should design reliable high-performance multipliers. The multiplier has the capacity to provide greater throughput with the variable latency and may adjust the AHL circuit to mitigate performance degradation that is a result of the maturing effect. Furthermore, the suggested architecture does apply to some column- or row-bypassing multiplier. Our suggested architecture with 16 × 16 and 32 × 32 row-bypassing multipliers is capable of as much as 80.17% and 69.40% performance improvement as in comparison with 16×16 and 32 × 32 fixed-latency row-bypassing multipliers.

Key Words: Adaptive hold logic (AHL), negative bias temperature instability (NBTI), reliable multiplier, variable latency, digital multiplier (DM).

## 1.INTRODUCTION:

The throughput of those programs is dependent on multipliers, and when the multipliers are extremely slow, the performance of entire circuits will disappear [1]. Digital multipliers are some of the most important arithmetic functional models in lots of programs, like the Fourier transform, discrete cosine transforms, and digital filtering. In addition, negative bias temperature instability happens whenever a pMOS transistor is under negative bias. In cases like this, the interaction between inversion layer holes and hydrogen-passivity Si atoms breaks the Si-H bond produced throughout the oxidation process, producing H or H2 molecules. When these molecules diffuse away, interface traps remain. The accrued interface traps between plastic and also the gate oxide interface lead to elevated threshold current, lowering the circuit switching speed [2]. Once the biased current is taken away, overturn

reaction happens, lowering the NBTI effect. However, overturn reaction doesn't eliminate all of the interface traps produced throughout the stress phase, and it is elevated within the lengthy term. Hence, you should design a dependable high-performance multiplier. The related impact on an nMOS transistor is positive bias temperature instability which happens when an nMOS transistor is under positive bias. A conventional approach to mitigate the maturing effect is overdesign including things like guard-banding and gate oversizing however, this method can be quite pessimistic and area and power inefficient. To avert this problem, many NBTI-aware methodologies happen to be suggested. An NBTI-aware technology mapping technique was suggested to be sure the performance from the circuit during its lifetime. An NBTI-aware sleep transistor is built to lessen the aging effects on pMOS sleeptransistors, and also the lifetime stability from the power-gated circuits in mind was enhanced [3]. Traditional circuits use critical path delay because the overall circuit clock cycle to be able to perform properly. However, the probability the critical pathways are triggered is low. Generally, the road delay is shorter compared to critical path. Of these noncritical pathways, while using critical path delay because the overall cycle period can lead to significant timing waste. Hence, the variable-latency design was suggested to lessen the timing waste of traditional circuits. The variable-latency design divides the circuit into a double edged sword, shorter pathways and longer pathways. Shorter pathways can execute properly in a single cycle, whereas longer pathways need two cycles to complete. When shorter pathways are triggered frequently, the typical latency of variablelatency designs is preferable to those of traditional designs. A brief path activation function formula was suggested to enhance the precision from the hold logic and also to optimize the performance from the variable-latency circuit. A flexible-latency pipelined multiplier architecture having a Booth formula was suggested. These research designs could lessen the timing waste of traditional circuits to enhance performance, but they didn't think about the aging effect and may not adjust themselves throughout the runtime. A flexible-latency adder design that views the

Volume: 03 Issue: 09 | Sep-2016

www.irjet.net

execution result utilizing a postponed clock signal, that is reduced compared to normal clock signal. If errors occur, the Razor switch-flop sets the mistake signal to at least one to inform the machine to execute the operation and inform the AHL circuit that the error has happened.

e-ISSN: 2395 -0056

p-ISSN: 2395-0072

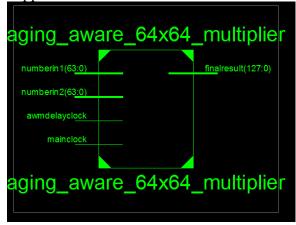

Fig.1 rtl schematic 1

We use Razor switch-flops to identify whether a surgical procedure that is regarded as a 1-cycle pattern can definitely finish inside a cycle. Even though the execution may appear pricey, the total cost is low since the execution frequency is low. More particulars for that Razor switch-flop are available [5]. The AHL circuit is paramount component within the aging-ware variable-latency multiplier the particulars from the AHL circuit. The AHL circuit consists of a maturing indicator, two knowing blocks, one mux, and something D switch-flop. The maturing indicator signifies if the has endured significant performance degradation because of the aging effect. The maturing indicator is implemented inside a simple counter that counts the amount of errors over some procedures and it is reset to zero in the finish of individuals procedures. This timing violation is going to be caught through the Razor switch-flops, which generate error signals. Both are used to decide whether a port pattern requires a couple of cycles, only one of these is going to be selected at any given time.

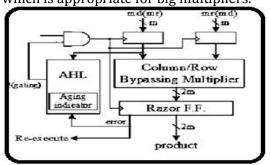

maturing effect was suggested. However, no variablelatency multiplier design that views the maturing effect and may adjust dynamically continues to be done. We advise a maturing-aware reliable multiplier design having a novel adaptive hold logic (AHL) circuit. The multiplier is dependent on the variable-latency technique and may adjust the AHL circuit to attain reliable operation drunk of NBTI and PBTI effects. To be precise, the contributions of the paper are summarized the following: novel variable-latency multiplier archit-ecture by having an AHL circuit. The AHL circuit can decide if the input designs require a couple of cycles and may adjust the knowing criteria to make sure that there's minimum performance degradation after considerable aging happens comprehensive analysis and comparison from the multiplier's performance under different cycle periods to exhibit the potency of our suggested architecture a maturing-aware reliable multiplier design way in which is appropriate for big multipliers.

Fig.1. Block diagram of Proposed System II. IMPLEMENTATION

It introduces the general architecture and also the functions of every component as well as describes how you can design AHL that changes the circuit when significant aging happens. Suggested aging-aware multiplier architecture [4]. The inputs from the rowbypassing multiplier would be the symbols within the parentheses. Within the suggested architecture, the column-and row-bypassing multipliers could be examined by the amount of zeros either in the multiplicand or multiplication to calculate if the operation requires one cycle or two cycles to accomplish. Based on the bypassing selection within the columnar row-bypassing multiplier, the input signal from the AHL within the architecture using the column-bypassing multiplier may be the multiplicand, whereas those of the row-bypassing multiplier may be the multiplication. Razor switch-flops may be used to identify. The primary switch-flop catches the execution result for that combination circuit utilizing a normal clock signal, and also the shadow latch catches the

## **International Research Journal of Engineering and Technology** (IRJET)

**Volume:** 03 **Issue:** 09 | **Sep-2016** www.irjet.net p-ISSN: 2395-0072

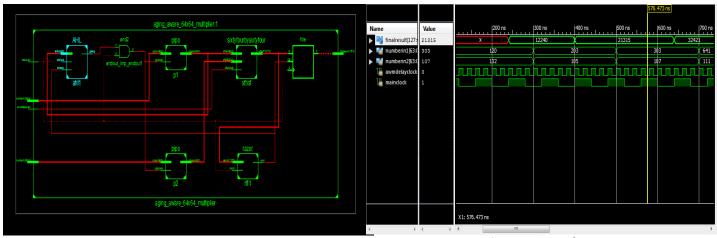

Fig.2 rtl schematic 2

In comparison using the first knowing block, the 2nd knowing block enables a smaller sized quantity of designs to get one-cycle designs since it requires more zeros within the multiplicand. The particulars of the whole process of the AHL circuit are listed below: when a port pattern arrives, both knowing blocks will decide if the pattern requires one cycle or two cycles to accomplish and pass both leads to the multiplexer. The multiplexer chooses certainly one of either result in line with the creation of the maturing indicator. The general flow in our suggested architecture is really as follows: when input designs arrive, the column- or row-bypassing multiplier, and also the AHL circuit execute concurrently. The Razor switch-flops check whether there's the road delay timing breach. Thus, the Razor switch-flops will output a mistake to tell the machine the current operation must be executed using two cycles to guarantee the operation is true. In cases like this, the additional execution cycles brought on by timing breach incurs a problem to overall average latency. However, our suggested AHL circuit can precisely anticipate whether the input designs require a couple of cycles generally. In conclusion, our suggested multiplier design has three key features. First, it's a variable-latency design that minimizes the timing waste from the noncritical pathways. Second, it may provide reliable procedures despite the maturing effect happen. The Razor switch-flops identify the timing violations and execute the procedures using two cycles. Finally, our architecture may change the proportion of 1-cycle designs to reduce performance degradation because of the aging effect. Once the circuit is aged, and lots of errors occur, the AHL circuit uses the 2nd knowing block to determine if the input is a cycle or two cycles.

Fig.3 output waveform

e-ISSN: 2395 -0056

## III. CONCLUSION

This paper suggested a maturing-aware variablelatency multiplier design using the AHL. The multiplier has the capacity to adjust the AHL to mitigate performance degradation because of elevated delay. In addition, our suggested architecture using the 16×16 and 32×32 rowbypassing multipliers is capable of as much as 80.17% and 69.40% performance improvement in comparison using the  $16 \times 16$  and  $32 \times 32$  FLRB multipliers. Observe that additionally towards the BTI effect that increases transistor delay, interconnect also offers its aging issue that is known as electro migration. Electro migration happens once the current density is sufficient to result in the drift of metal ions across the direction of electron flow. The metal atoms is going to be progressively displaced after some time, and also the geometry from the wires can change. If your wire becomes narrower, the resistance and delay from the wire is going to be elevated, as well as in the finish, electro migration can lead to open circuits. This problem can also be more severe in advanced process technology because metal wires are narrower, and alterations in the wire width may cause bigger resistance variations. When the aging effects brought on by the BTI effect and electro migration are thought together, the delay and gratification degradation could be more significant. Fortunately, our suggested variable latency multipliers may be used drunk of both BTI effect and electro migration. Additionally, our suggested variable latency multipliers tight on performance degradation because variable latency multipliers tight on timing waste, but traditional multipliers have to think about the degradation brought on by both BTI effect and electro migration and employ the worst situation delay because the cycle period.

## REFERENCES

[1] H.-I. Yang, S.-C. Yang, W. Hwang, and C.-T. Chuang, "Impacts of NBTI/PBTI on timing control circuits and degradation tolerant design in nanoscale CMOS SRAM," *IEEE Trans. Circuit Syst.*, vol. 58, no. 6, pp. 1239–1251, Jun. 2011.

[2] M. Basoglu, M. Orshansky, and M. Erez, "NBTI-aware DVFS: A new approach to saving energy and increasing

# $\textbf{International Research Journal of Engineering and Technology} \ (\texttt{IRJET})$

Volume: 03 Issue: 09 | Sep-2016 www.irjet.net p-ISSN: 2395-0072

processor lifetime," in *Proc. ACM/IEEE ISLPED*, Aug. 2010, pp. 253–258.

- [3] D. Mohapatra, G. Karakonstantis, and K. Roy, "Low-power processvariation tolerant arithmetic units using input-based elastic clocking," in *Proc. ACM/IEEE ISLPED*, Aug. 2007, pp. 74–79.

- [4] D. Baneres, J. Cortadella, and M. Kishinevsky, "Variable-latency design by function speculation," in *Proc. DATE*, 2009, pp. 1704–1709.

- [5] B. C. Paul, K. Kang, H. Kufluoglu, M. A. Alam, and K. Roy, "Negative bias temperature instability: Estimation and design for improved reliability of nanoscale circuit," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 26, no. 4, pp. 743–751, Apr. 2007.

e-ISSN: 2395 -0056