# Design and Simulation of a 16kb Memory using Memory Banking

# technique

# Akhilesh Tiwari<sup>1</sup>, Soumitra S Pande<sup>2</sup>

<sup>1</sup>Scholar, M.Tech VLSI, IMEC, Sagar (M.P.)India <sup>2</sup>Assistant Professor, EC Department, IMEC, Sagar (M.P.)India \*\*\*

**Abstract** - Monolithic architecture gives better performance up to in the order of Kb whereas for the bigger memory designs like Mb, the monolithic architecture will not give better performance. As the number of cells increases then the bit line and word line parasitic capacitances increases, hence unwanted delays increases, this in turn reduces the operating frequency. So in the design of bigger memories Memory Banking method is used which gives better performance compared to monolithic architecture.[7] The operating frequency of memory is reduced by a factor two as the number of rows doubles whereas the frequency of operation is reduced by a factor of four as the number of columns doubles. Hence memory banking which is also known as array portioning technique is used in the design of bigger size memories. In industries, the design of bigger memories whose size is around *Gb, can be done by using some scripting languages like Perl,* SKILL. This paper gives the design of a 16kb memory with the help of memory banking technique.

Key Words: Architecture, capacitances, delays, monolithic, memory banking.

#### **1.INTRODUCTION**

Memory partitioning is the procedure of tiling memory arrays and putting the tiles in memory such that a greatest number of data gets to are fulfilled from local memory. Memory banking is broadly embraced to proficiently increase the memory data transmission by utilizing various memory banks and diminishing data access conflict. Banking distributed arrays to guarantee the locality of reference is broadly perceived as being critical in getting great execution on circulated memory processors. Memory banking has been considered in the distributed registering domain for quite a long time [8, 10, 12], where information components are divided into distinctive processors to diminish communication among the processors. In memory banking method the large array is divided in to number of sub arrays which are identical in size. The sub arrays are commonly referred as macros, which stores the part of the data known as sub word. In order to get complete Word all the sub arrays are accessed simultaneously. To design High performance SRAM the number of macros is limited to around 16 whereas for low power SRAM design the number of macros are limited to only one. [7]

#### 2. DWL TECHNIQUE

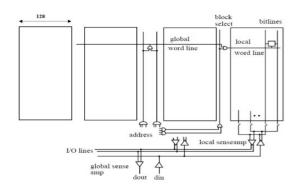

In DWL technique the Monolithic array is partitioned into m number of blocks and each block is operated independently hence the word line length is reduced by a factor of m, so the word line RC delay is reduced by a factor of . Hence the frequency of operation is increased by a factor compared to monolithic architecture. The figure 1 shown below depicts the DWL architecture. In that 512 columns are divided into 4 blocks with block size of 128 columns. Now two stages of selection is required to access particular row. First one is a global word line, which is used to select one of the four blocks and second one is local word line which is used to select desired word line. The local word line which are having only 128 columns, hence its RC delay reduces. In spite of the fact that the global word line still is almost the length of the width of the macro it has lower delay compared to full word line because the capacitive load of global word line is smaller. It only consider the input loading of only four global word lines rather than complete loading of 512 cells. And at a time only one block i.e. 128 cells are activated rather than complete memory i.e. 512 cells hence the column current is reduced by a factor of four. The concept of DWL is used recursively in the design of bigger memory leads to hierarchical word line decoding technique.

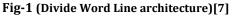

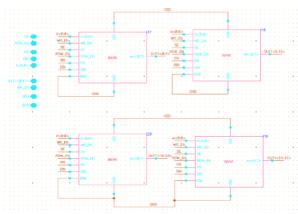

In this paper 16-Kb SRAM Based memory is designed by using banking method, in which four banks are used with size of each bank is 4Kb. The layout of 16-Kb memory is drawn and post layout simulations also completed for the complete memory. The reason for the Memory Banking architecture presented in this project is to enhance the performance of a system by relegating memory accesses to the disjoint memory banks and giving synchronous clash-free memory accesses. The fig 2 shows the banking architecture for 16-Kb memory. is selected by using a column 4to1 multiplexer. Hence total eight 4to1 multiplexers are required in the design of 4Kb memory bank.

Fig -2: 16Kb memory using banking method

#### 3. DESIGN OF 4KB MEMORY BANK

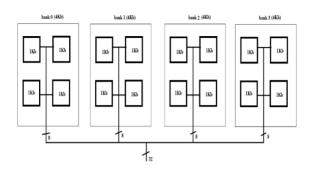

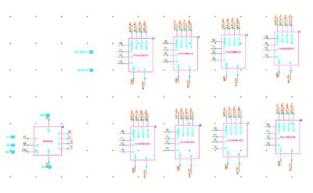

Fig - 3 Schematic of 4Kb Memory Bank

Fig 4 - Schematic of Bank Multiplexer of 4-Kb Memory

Fig 5: Layout of Bank Multiplexer of 4Kb Memory Bank

Fig 6: Layout of 4Kb Memory Bank

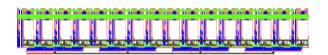

Fig 7: Av-Extracted View of 4Kb Memory Bank

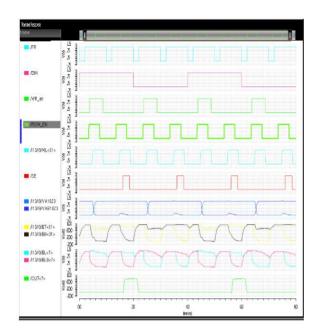

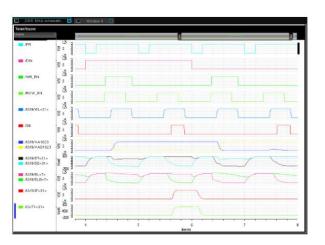

Fig 8: Simulation Results of 4Kb Memory Bank

Table 1: Power Analysis of 4Kb Memory Bank

| S.No | Description           | Pre-Layout   | Post-                 |

|------|-----------------------|--------------|-----------------------|

|      |                       | Simulations  | Layout<br>Simulations |

| 1    | Write 1 power         | 14.19 p Watt | 16.11 p<br>Watt       |

| 2    | Read 1 power          | 14.07 p Watt | 15.37 p<br>Watt       |

| 3    | Write 0 power         | 14.36 p Watt | 16.63 p<br>Watt       |

| 4    | read 0 power          | 14.33 p Watt | 15.67 p<br>Watt       |

| 5    | Total transient power | 57.01 p Watt | 80.10 p<br>Watt       |

| 6    | frequency             | 1.25 Ghz     | 1Ghz                  |

# 4. DESIGN OF 16kb MEMORY BANK

Fig 9: Schematic of 16-Kb Memory

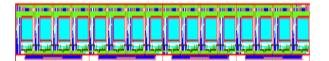

Fig 10: Layout of 16Kb Memory

Fig 12: Simulation results of 16kb SRAM Memory

# 5. CONCLUSIONS

In this paper design and simulation of 4kb Memory and 16 Kb memory has been studied. 16-Kb Memory is designed using banking method with data width of 32 bits and it takes 1ns for one complete operation hence frequency of operation is calculated as 1 GHz.

# 6. REFERNCES

[1]. Sung-Mo Kang and Yusuf Leblebici ||CMOS Digital Integrated Circuits||, TATA McGRAW-HILL EDITION 2003 and research work of Sarika Anil Kumar, NIT-K May 2015.

[2]. Jan M.Rabaey Anantha Chandrakasan Borivoje Nikolic ||Digital Integrated Circuits||, Pearson Education Electronics ,2003.

[3]. Debasis Mukherjee,Hemanta Kr.Mondal,||Static Noise Margin Analysis of SRAM Cell For High Speed Application||, IJCSI International Journal of Computer Science Issues, Vol. 7,Issue 5,September 2010.

[4]. N. C. Li, et. al., —CMOS tapered buffer||, IEEE Journal of Solid State Circuits, vol.25, no. 4, pp. 1005-1008, August 1990.

[5]. J. Choi, et. al., —Design of CMOS tapered buffer for minimum power-delay product||, IEEE Journal of Solid State Circuits, vol. 29, no. 9, pp. 1142-1145, September 1994.

[6]. B. S. Cherkauer and E. G. Friedman, —A unified design methodology for CMOS tapered buffers||, IEEE Journal of Solid State Circuits, vol. 3, no. 1, pp. 99-110, March 1995.

[7]. M. Yoshimoto, et. al., —A 64kb CMOS RAM with divided word line structure||, 1983 IEEE International Solid State Circuits Conference, Digest of Technical Papers, pp. 58-59.

[8]. The Invention of the Intel 1103 - The World's First AvailableDRAMChipByMaryBellis||[Online].

Availabe:http://inventors.about.com/library/weekly/aa100898.ht ml

[9]. T. Wada, et al., -An analytical access time model for on-chip cache memories, || IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 27. NO. 8, AUGUST 1992.

[10]. S. Verdoolaege, H. Nikolov, and T. Stefanov, "pn: A Tool for Improved Derivation of Process Networks," EURASIP Journal on Embedded Systems, vol. 2007, pp. 1-13, 2007.

[11]. Katsuro Sasaki, Kiyotsugu Ueda, Koichi Takasugi, et al, || A 16-Mb CMOS SRAM with a 2.3  $\mu$  Single-Bit-Line Memory Cell || IEEE Journal Of Solid-State Circuits, Vol. 28, No. 11, November 1993.

[12]. Rakesh Dayaramji Chandankhede – Design of High Speed Sense Amplifier for SRAM||, 2014 IEEE International Conference on Advanced Communication Control and Computing Technologies (ICACCCT).

[13]. Kunihiko Yamaguchi, Hiroaki Nambu, et. al. – A 1.5-ns Access Time, 78-pm' Memory-Cell Size, 64-kb ECL-CMOS SRAM||, IEEE Journal of Solid-State Circuits, Vol. 27, No.2. February 1992

[14]. Sreerama Reddy G M, P Chnadrasekhara Reddy, ||Design and implementation of 8Kbits Low Power SRAM in 180nm Technology ||,Proceedings of the International MultiConference of Engineers and Computer Scientists 2009 Vol II IMECS 2009, March 18-20, 2009

[15]. K. Khare, N. Khare, V. Kulhade and P. Deshpande, --VLSI Design And Analysis Of Low Power 6T SRAM Cell Using Cadence Tool," leSE, lohor Bahru, Malaysia, 2008.

[16]. Taehui Na, S. Woo, J. Kim, H. Jeong, and S. Jung, -Comparative Study of Various Latch- Type Sense Amplifiers, || IEEE Trans. On VLSI Systems, vol. 22, no. 2, pp. 425-429, Feb. 2014.

[17]. Ya-Chun Lai and Shi-Yu Huang, -A Resilient and Power-Efficient Automatic Power down Sense Amplifier for SRAM Design, IEEE Trans. On Circuits & Systems, vol. 55, no. 10, pp. 1031-1035, Oct. 2008.

[18]. K.W. Mai, et al. –Low-power SRAM design using half-swing pulse-mode techniques||, IEEE Journal of Solid State Circuits, vol. 33, no. 11, pp. 1659-1671, November 1998.

[19]. S. E. Schuster, et. al., -A 15-ns CMOS 64K RAM||, IEEE Journal of Solid State Circuits, vol. sc-21, no. 5, p. 704-711, October 1986.

- [20]. www.cypress.com

- [21]. www.wikipedia.org

- [22]. www.nptel.ac.in

[23]. Achiranshu Garg and Tony Tae-Hyoung Kim || SRAM Array Structures for Energy Efficiency Enhancement||, IEEE

TRANSACTIONS ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, VOL. 60, NO. 6, JUNE 2013

[24]. Byung-Do Yang – A Low-Power SRAM Using Bit-Line Charge-Recycling for Read and Write Operations||, IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 45, NO. 10, OCTOBER 2010

[25]. Koichi Takeda, Yasuhiko Hagihara, et.al, - A Read-Static-Noise-Margin-Free SRAM Cell for Low-VDD and High-Speed Applications||, IEEE JOURNAL OF SOLID STATE CIRCUITS, VOL. 41, NO. 1, JANUARY 2006.

#### SOUMITRA S PANDE,

Assistant Professor, IMEC Sagar, is an Instrumentation Graduate with Masters in VLSI Design. He has published more than 15 Research papers in renowned journals across the globe. His area of interest are

VLSI Design, Nano Relays etc. He has also guided more than 10 Master Degree dissertations in the subject field.