## **Drain Current and Radiation Relation for MOSFET**

Sonal Dahiya<sup>1</sup> Krishan Kumar<sup>2</sup>, <sup>1,2</sup>,Assistant Professor, ASET Amity University Haryana,Gurgaon, India \*\*\*

**Abstract** - This paper provides an overview on the basic physical mechanisms causing radiations and their effects on MOSFET parameters such as threshold voltage, drain current etc., when a MOS device is subjected to the radiations. The effect of radiation on MOSFET is studied for two different channel lengths.

Key Words: Radiation, Drain Current, MOSFET.

### I. INTRODUCTION

Space environment is hostile to most integrated electronic components. The radiation generally encountered in space are alpha, beta, gamma, X-ray, energetic electrons, protons, neutrons and ions og various kinds are prevalent in space and have potential to cause various transient or fatal device damages. MOSFET is the basic component of VLSI and ULSI circuits. Large packing density, low noise and low power requirement make MOS transistors superior to bipolar junction transistors. Unfortunately, MOS devices are susceptible to degradation in presence of ionizing radiation. Conventional MOSFET can survive 3-10 krad of total dose without much parametric degradation. However, ionizing radiation dose in excess of 50 krad may turn out to be fatal to these devices.

The Si-MOSFET has become the dominant device for ultra large scale integration (ULSI). The steady thrust of the IC industry is towards faster signal processing and more information handling capability per unit volume. As the interest and the effort continue in scaling down the device geometry to achieve higher speed, larger scale of integration and lower power consumption, we are constantly challenged by short channel length effects as the channel length is pushed down to deep submicron levels. Integration of billions of transistors in a single chip beyond the year 2000 will require device dimensions to be reduced below 0.1  $\mu$ m. Degradation of the threshold voltage, drain current and transconductance are the dominant small geometry effects limiting the scaling of the device dimensions.

The study of effect of nuclear radiation on short channel MOSFET assumes importance as these devices are susceptible to ionizing radiation and are widely used in the

electronic parts of the spacecraft and nuclear reactor where they must function properly in the radiation environment. The study of MOSFET under the influence of ionizing radiation has been an active area of research for past three decades .The interaction of ionizing radiation with materials and interfaces is quite complex. It is known that in MOSFET, radiation causes a change in the threshold voltage, current drives and trans conductance resulting in degradation of the device performance. The degradation depends on the total dose received by the device. One of the major effects of ionizing radiation in MOS devices is the generation of the electron-hole pairs in the oxide layer because of high energy of the incident radiation. The incident radiation would result in the formation of an electron-hole pair (EHP). The radiation induced electrons are much more mobile than the holes and swept out of the oxide layer very fast ( $\sim 1$  ps) under the influence of strong transverse electric field. The holes that are relatively immobile cause a negative shift of the flat-band voltage in the electrical characteristics of MOS devices. The other effect arises from the interaction of the radiation with the Si-SiO2 interface traps. When Si is thermally oxidized, the interface between the amorphous oxide and the crystalline Si is generally deficient of oxygen which gives rise to strained as well as `dangling' bonds. These `dangling' bonds act as interface traps with energy level within the forbidden bandgap at the Si-SiO2 interface. In presence of nuclear radiation, there is an increase in interfaces trapped charges at the Si-SiO2 interface when the radiation dose is comparatively high (dose in excess of 100 krad.

#### **II. RADIATION MECHANISMS**

Semiconductor devices are affected by two basic radiation damage mechanisms:

(i) Displacement damage: Incident radiation displaces silicon atoms from their lattice sites. The resulting defects alter the electronic characteristics of the crystal. An incident particle or photon capable of imparting an energy of about 20 eV to a silicon atom can dislodge it from its lattice site. Displacement damage creates defect clusters. For example, a 1 MeV neutron transfers about 60 to 70 keV to the Si recoil

atom, which in turn displaces roughly 1000 additional atoms in a region of about 0.1 mm size. Displacement damage is proportional to non-ionizing energy loss, which is not proportional to the total energy absorbed, but depends on the particle type and energy.

(ii) Ionization damage: Energy absorbed by electronic ionization in insulating layers, predominantly SiO2, liberates charge carriers, which diffuse or drift to other locations where they are trapped, leading to unintended concentrations of charge and, as a consequence, parasitic fields. The ionization damage consists of four processes:

- (a)Electron hole pair generation

- (b) Transport of the holes to the Si/SiO2 interface

- (c) Deep hole trapping

- (d) Radiation induced interface traps

# III. EFFECT OF RADIATION ON THE ELECTRICAL PARAMETERS

In this section we present the consequences of hole trapping in the oxide and of interface traps generation on the electrical parameters of a MOS transistor, namely threshold voltage VT, the subthreshold current and the leakage current, the carrier mobility u and the transconductance g<sub>m</sub>.

#### (i)Threshold voltage shift

These shifts are the result of the additional positive oxide traps and interface traps from radiation exposure, and thus the shifts can be broken down into individual contributions from each type of trap. While positive oxide traps are not the main focus of this work, it is still important to at least consider them when relating the shifts due to interface traps. Typically, MOS transistors operate under strong inversion where the gate bias is larger than the threshold voltage of the device. Under such conditions, interface traps in n-MOS transistors tend to contribute negative charge to the conduction band and thus exhibit a positive shift in the threshold voltage. Conversely, under similar conditions, the interface traps in a p-MOS transistor tend to contribute positive charge resulting in an effective negative shift in the threshold voltage. The relationship between the concentration of interface states at the oxide-silicon boundary, Nit, and the threshold shift,  $\Delta VTH$  or  $\Delta Vit$ ,

$$\Delta V_{TH} = \Delta V_{it} = \frac{q}{C_{ox}} \Delta N_{it}$$

where Cox is the capacitance per unit area The threshold voltage shift component associated with the radiation induced interface states  $\Delta N$  it can be treated as

$$\Delta N_{\rm it} = k_{\rm g} f_{\rm y} D(E) t_{\rm ox} f_{\rm it}$$

Where kg is the number of electron-hole pairs produced per unit dose, fy is the probability that an electron -hole pair escapes recombination, D(E) is the incident radiation dose shown as a function of energy(E) and fit is the number of interface-trapped charges created per radiation-induced electron-hole pair Vit can have positive or negative values. We assume that the traps above midgap are acceptor-like and those below are donor-like. This means that for an nchannel transistor (for example), where the Fermi level in the silicon close to the silicon-oxide interface lies between Ei and Ec, the acceptor-like traps which are below the Fermi level will be negatively charged, and then the threshold voltage shift will be positive. Similarly for a p-channel the threshold voltage shift will be negative (i.e. the threshold voltage increases, in absolute value, both for an n-channel transistor and for a p-channel

#### (ii) Increase of subthreshold currents

The "off-state" current in a MOS transistor is defined as the current which flows from drain to source when VGS = 0, and is sometimes referred to as "leakage current". In an irradiated n-channel transistor two effects lead to an increase in the "off-state" current: the increase of the subthreshold current and the generation of parasitic currents. These phenomena can be critical for many applications, as for example when the transistor is used as a switch. The increase in the subthreshold current is related to two factors, illustrated infig. The first is the decrease of the threshold voltage. The pre-irradiation solid line in fig. 1.10 shifts towards the y axis (VT goes from VT1 to VT2) and becomes the dotted line after irradiation. The second is the radiation-induced decrease of the subthreshold slope due to this effect the dotted line in figure 1.10 becomes the solid one after irradiation. The subthreshold current which before irradiation was I1 becomes therefore I2 due to the threshold voltage shift and then I3 due to the subthreshold slope decrease.

#### (iii) Decrease of mobility and transconductance

The mobility degradation after irradiation is essentially related to the increase of the interface traps, since the conduction in an MOS transistor is due to the carrier motion close to the silicon-oxide interface. As shown in eq the mobility trend as a function of the increase of the traps can be expressed by the following empirical formula

$$\mu = \frac{\mu_0}{1 + \alpha \left(\Delta N_{it}\right)}$$

where  $\mu$  is the pre-irradiation mobility,  $\Delta N$  it is the increase of the interface traps and  $\alpha$  is a parameter whose value depends on the technology. The degradation of the mobility gives origin to degradation in the transconductance, which is proportional to  $\mu$  in the linear region and to  $\mu 1/2$  (for a constant current) in saturation. This decreases the driving capability of the device.

#### **IV. Results**

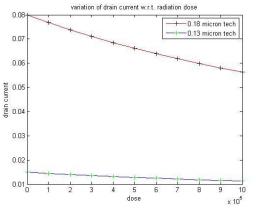

The figure 1 shows the variations of drain current with respect to radiation dose in two technologies. The drain current constitute all the factors such as threshold voltage shift, mobility of charge carriers and interface trapped charge. From the above figure it is concluded that the curve of 0.13  $\mu$ m technology is more stable than the 0.18  $\mu$ m technology.

Fig 1 Variations of drain current with respect to radiation dose

#### V. Conclusion

With feature sizes ranging from 200 nm to 90 nm, today's very deep submicron technologies pose new modeling challenges including power dissipation, leakage management, and short channel effects in deep submicron transistors, increasing capacitive and inductive noise in interconnect and platform integration issues. With this regard device models are constantly developed, elaborated and refined to achieve best description and prediction of the downscaling devices. By comparing results of two different technologies i.e. 0.13  $\mu$ m and 0.18  $\mu$ m it is concluded 0.13  $\mu$ m

technology is less susceptible to the radiations as compared to the 0.18  $\mu m$  technology.

#### VI. References

- Bijan davari, Robert H Dennard, Ghavam, "CMOS scaling for high performance and low power – The Next ten years", IEEE VOL 83 No. 4 April 1995

- 2. R.K. Chauhan, P.Chakrabarti, "Effect of ionizing radiation on MOS capacitors", Department of electronics engg, October 2001

- R K Chauhan, S Dasgupta and P Chakrabarti, "A pseudo-two-dimensional model of an n-channel MOSFET under the influence of ionizing radiation" , July 2002

- 4. Yee-Chia Yeo, Tsu-Jae King and Chenming Hu, "MOSFET Gate Leakage Modeling and Selection Guide for Alternative Gate Dielectrics Based on Leakage Considerations", IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 50, NO. 4, APRIL 2003

- T. R. Oldham & F. B. McLean, "Total Ionizing Dose Effects in MOS Oxides and Devices", IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 50, NO. 3, JUNE 2003

- H. L. Hughes and J. M. Benedetto, "Radiation Effects and Hardening of MOS Technology: Devices and Circuits", IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 50, NO. 3, JUNE 2003 Dr. Danny Rittman, "CMOS Nanometer scaling, Limited!", July 2006.

- T.K. Maiti, S.S. Mahato, P. Chakraborty, S. K. Sarkar, and C. K. Maiti, "Radiation Effects on Strain-Engineered pmosfet", IEEE 2007

- Vincent Goiffon, Pierre Magnan, Fr'ed'eric Bernard, Guy Rolland, " Ionizing Radiation Effects on CMOS Imagers Manufactured in Deep Submicron Process", Universit'e de Toulouse, ISAE, 10 avenue E. Belin, 31055, Toulouse, France

- E. Simoen1, J.M. Rafí1, A. Mercha, Serra-Gallifa1, H. van Meer," Radiation Damage in Deep Submicron Partially Depleted SOI CMOS", E.E. Dept, KU Leuven, Belgium