# **Design of Pulsed latch Shift register**

Veeresh Gavai<sup>1</sup>, Mrs. Veeramma Yatnalli<sup>2</sup>, Mrs. Saroja S Bhusare<sup>3</sup>

<sup>1</sup> VLSI design and Embedded system(MTech) JSSATE Bengaluru <sup>2,3</sup> Associate Professor, JSSATE Bengaluru Department of Electronics and Communication Engineering \*\*\*

**Abstract** - The design and implementation of Shift register with consumption of less power and less area occupation by latches. Basically shift registers are built by flip flops but here flip flops are replaced by pulsed latches to reduce area power consumption. The problem of timing in latches is removed by using the compound non overlie clock signals which are delayed instead of standard clock pulse. A 256 bit shift registers are designed in cadence virtuoso using gpdk 180nm technology and VDD=1.8v and the SSASPI latch is compared with other latches.

Key Words: Pulsed latch, pulsed clock, shift register, flip flop etc..

## **1. INTRODUCTION**

Shift register are employed in many applications, such as digital filters, communication receivers and image processing Ic's because they are basic building blocks in VLSI circuits . Recently because the size of the image data has increasing heavily due to the demand for high quality image data, word length of shift register growing to manage large number of image data in image processing ICs. As we know the word length of the shifter register increases, the power consumption and area of the shift register becomes more vital design considerations.

The design of a register is very easy. An n-bit register consist of serially attached n data FFs. The occupation of area and consumption of power are more vital than performance of FF as result there is no circuit between flip flop within shift registers. Recently, to cut down the consumption if power and occupation of area FFs have been taken down by pulsed latches in various functions, because latches are very much minor compared to flip-flop. But the pulsed latches are suffering from timing problem between pulsed latches. Here the shit registers are built with low power and using pulsed latches. The problem of timing within the latches are changed by compound non overlie clock pulses which are delayed rather than traditional single pulsed clock signal.

# 2. SHIFT REGISTER

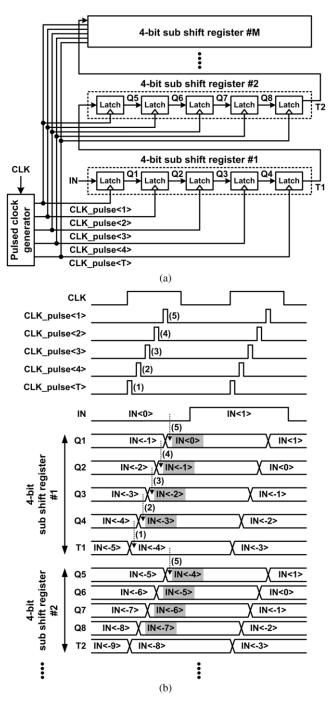

Shift register is divided into sub shifter registers to reduce the number of delayed pulsed clock signals. A 4-bit sub shifter register consists of five latches and it performs shift operations with five non-overlap delayed pulsed clock signals (CLK\_pulse1:4) and CLK\_pulseT). In the 4-bit sub shift register #1, four latches store 4-bit data (Q1-Q4) and the last latch stores 1-bit temporary data (T1) which will be stored in the first latch (Q5) of the 4-bit sub shift register #2. Delay circuits cause large area and power overheads.

Another solution is to use multiple non-overlap delayed pulsed clock signals, as shown in Figure (a). The delayed pulsed clock signals are generated when a pulsed clock signal goes through delay circuits. Each latch uses a pulsed clock signal which is delayed from the pulsed clock signal used in its next latch. Therefore, each latch updates the data after its next latch updates the data. As a result, each latch has a constant input during its clock pulse and no timing problem occurs between latches. However, this solution also requires many delay circuits. Fig. 5(a) shows an example the proposed shift register. The proposed shift register is divided into sub shifter registers to reduce the number of delayed pulsed clock signals. A 4-bit sub shifter register consists of five latches and it performs shift operations with five non-overlap delayed pulsed clock signals (CLK\_pulse1:4 and CLK\_pulseT). In the 4-bit sub shift register #1, four latches store 4-bit data (Q1-Q4) and the last latch stores 1bit temporary data (T1) which will be stored in the first latch (Q5) of the 4-bit sub shift register #2. Figure (b)shows the operation waveforms in the proposed shift register. The proposed shift register reduces the number of delayedpulsed clock signals significantly, but it increases the number of latches because of the additional temporary storage latches. As shown in Fig. 6 each pulsed clock signal is generated in a clock-pulse circuit consisting a delay circuit and an AND gate. When an shift register is divided into sub shift registers, the number of clock-pulse circuits is and the number of latches is. A sub shift register consisting of latches requires pulsed clock signals.

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

Figure1 Proposed Shift register

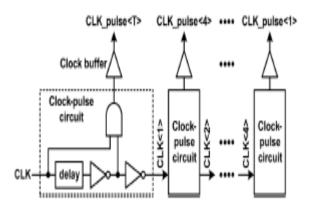

### 2.1 Pulsed Clock generation circuit

To get constant form of clock pulse the summing up of all inverters rising and falling times within the circuits of delay should be less than typical delayed clock pulsed clock circuit. However in fig2 the summing up of inverters rising and falling times are longer than within clock pulse generator with the effect of delay, the periodic dimension are often because And circuit is used to produce the very sharp pulse and 2 signals which are delayed. Therefore, for short pulse signals the pulse generation circuit is suitable.

Fig2 Pulse generation circuit

### **3 IMPLEMENTATION**

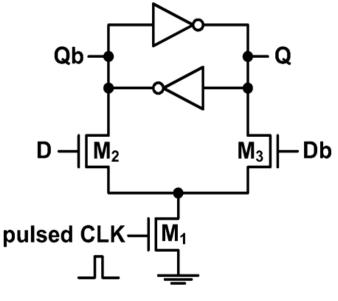

In chip implementation, the SSASPL (static differential sense amp shared pulse latch) in Figure 3, which is the smallest latch, is selected. The original SSASPL with 9 transistors [6] is modified to the SSASPL with 7 transistors in Fig. 8 by removing an inverter to generate the complementary data input (Db) from the data input (D). In the proposed shift register, the differential data inputs (D and Db) of the latch come from the differential data outputs (Q and Qb) of the previous latch. The SSASPL uses the smallest number of transistors (7 transistors) and it consumes the lowest clock power because it has a single transistor driven by the pulsed clock signal.

The SSASPL latch is designed and simulated with 180nm technology at VDD= 1.8v.

Figure3 SSASPL latch.

International Research Journal of Engineering and Technology (IRJET) Volume: 04 Issue: 05 | May -2017 IRJET

www.irjet.net

e-ISSN: 2395 -0056 p-ISSN: 2395-0072

# 4. RESULT

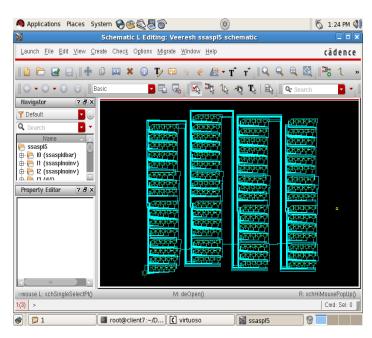

Fig Schematic of 256bit shift register

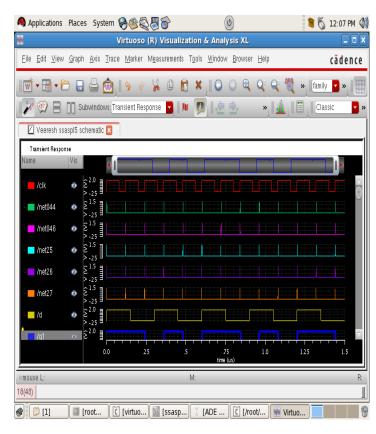

Fig Input of 256 bit shift register

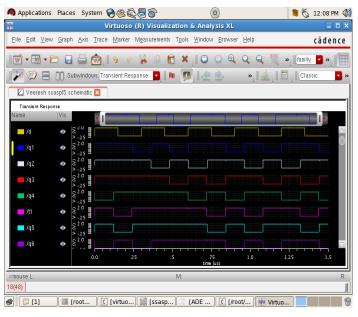

Fig Output of 256 bit shift register

# **5 COMPARISION**

Table 1 shows Comparison of power in (mW) between latches

| Sl | Latches          | Power  |  |

|----|------------------|--------|--|

| no |                  |        |  |

| 1. | PowerPC 603 MS   | 4.6mW  |  |

|    | latch[5]         |        |  |

| 2. | SSTC MS latch[5] | 3.56mW |  |

| 3. | DSTC MS          | 3.43mW |  |

|    | latch[5]         |        |  |

| 4. | HLFF[6]          | 3.37mW |  |

| 5. | SSALA[6]         | 2.78mW |  |

| 6. | SSASPL           | 1.9mW  |  |

Table 2 shows the number of transistor count in different latches

| Sl | latches  |    | No            | No of      |

|----|----------|----|---------------|------------|

| no |          |    | of transistor | transistor |

|    |          |    |               | connected  |

|    |          |    |               | to clock   |

| 1. | PowerPC  | MS | 18            | 8          |

|    | latch[5] |    |               |            |

| 2. | SSTC     | MS | 16            | 2          |

|    | latch[5] |    |               |            |

| 3. | DSTC     | MS | 9             | 2          |

|    | latch[5] |    |               |            |

| 4. | HLFF[6]  |    | 20            | 5          |

| 5. | SSALA[6] |    | 9             | 1          |

| 6. | SSASPL   |    | 7             | 1          |

Т

#### CONCLUSION

This paper proposes design and implementation of shift register using pulsed latches. The shift registers are built using latches which are smaller in size than flip flop. The schematic of 256 bit shift register is designed in Cadence tool with VDD =1.8v, power is calculated with respect to different latches.

#### REFERENCES

[1] S. Heo, R. Krashinsky, and K. Asanovic, "Activity-sensitive flip-flop and latch selection for reduced energy," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 9, pp. 1060-1064, Sep. 2007.

[2] S. Naffziger and G. Hammond, "The implementation of the nextgeneration 64 b itanium microprocessor," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2002, pp. 276-504.

[3] H. Partovi et al., "Flow-through latch and edge-triggered flip-flop hybrid elements," IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 138–139, Feb. 1996.

[4] E. Consoli, M. Alioto, G. Palumbo, and J. Rabaey, "Conditional push-pull pulsed latch with 726 fJops energy delay product in 65 nm CMOS," in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2012, pp. 482-483.

[5] V. Stojanovic and V. Oklobdzija, "Comparative analysis of masterslave latches and flip-flops for high-performance and low-power systems," IEEE J. Solid-State Circuits, vol. 34, no. 4, pp. 536–548, Apr. 1999.

[6] B.-S. Kong, S.-S. Kim, and Y.-H. Jun, "Conditional-capture flip-flop for statistical power reduction," IEEE J. Solid-State Circuits, vol. 36, pp. 1263–1271, Aug. 2001.

[7] J.-K. Kang, W. Liu, and R. K. Cavin III, "A CMOS high speed data recovery circuit using the matched delay sampling technique," IEEE Journal of Solid-State Circuits, vol. 32, no. 10, pp. 1588-1596, 1997.

[8]H. Kawaguchi and T. Sakurai, "A reduced clockswing flipflop (RCSFF) for 63% power reduction," IEEE J. Solid-State Circuits, vol.33, no. 5, pp. 807-811, May 1998.