## e-ISSN: 2395-0056

p-ISSN: 2395-0072

# FPGA Implementation of High Speed AMBA Bus Architecture for Image Transmission and Face Detection

## Akshaykumar Yalkar<sup>1</sup>, Ganapathi V Sagar<sup>2</sup>

<sup>1</sup>M.Tech student ,Department of EIE ,Dr.A.I.T ,Bengaluru-560056 <sup>2</sup>Assistant Professor , Department of EIE ,Dr.A.I.T ,Bengaluru-560056

**Abstract -** AMBA remains for Advanced Microcontroller Bus Architecture which is chiefly utilized for information synchronization between various sensors and additionally actuators and primary handling units. Typically the working pace of primary handling unit is substantially higher than any associated sensors as well as actuators. In any case, the handling unit must process those information with high exactness. For appropriate operation of the entire framework, the information speed of different associated gadgets must be synchronized. Typically this sort of information synchronization is finished by AMBA controller with the assistance of some measure of memory. Presently a day's different new sorts of use needs all the while perform read and compose operation on the memory. Be that as it may, the ordinary AMBA design does not bolster such conditions. In this way, in this venture we change the regular AMBA engineering to help such sort of utilizations. And furthermore the proposed configuration uses less measures of equipment assets than existing.

*Key Words:* AMBA-AHB,FPGA,AHB master ,AHB slave ,FSM, memory controller

#### 1. INTRODUCTION

Presently a day's life is fantastically brisk. to deal with brisk life human culture is fantastically a ton of ward to devices. Devices might have the capacity to play out a gathering of predefined assignment speedier than customary individual. however to shape faster contraptions, the procedure unit ought to have the capacity to technique the information document To make speedier process unit we will utilize snappier plan. however which won't settle the full drawback. because of the procedure speed furthermore depend upon how energetically data will reach to the real procedure unit. The causation of data is straightforwardly needy to the speed of the transport configuration blessing inside the style. configuration transport configuration straightforward assignment. because of the processor should take data from any information sensors which can initiate by some episode on that and that we comprehend that the measure of such occurrence is path longer than the recurrence is utilized by the processor. In this way, once we interface the gadget to the processor then recurrence coordinate happens. to beat that kind of drawback recurrence change i.e. low recurrence data to high

recurrence data at the contribution of processor and tight clamp versa inside the yield part of the processor.

- 1.1. Motivation: Now a day's different applications needs all the while read and compose of memory. Regularly those applications are executed utilizing AMBA transport because of distinction in working pace of every segment i.e. sensor, actuator and preparing components and so on. However, the customary AMBA engineering does not bolster such conditions. In this way, in this venture we will change the customary AMBA design to help such conditions.

- 1.2. Problem Definition: In live picture preparing applications, there is a bungle happens amongst camera and handling components working clock frequencies. Regularly the clock recurrence crisscross issue is comprehended by AMBA design by utilizing memory components which can work on various frequencies at read and compose cycles regulated by AMBA transport. Be that as it may, regular AMBA engineering does not bolster such conditions.

#### 1.1LITERATURE SURVEY

Shashisekhar et al., [1] arranged superior transport configuration utilized in fast data move in microcontroller. amid this paper a phenomenal playing expert/slave memory controller is planned and authorized abuse microcontroller transport outline. amid this paper AMBA Brobdingnagian playing transport ace slave adjacent to memory controller limit range unit talked. It conjointly gives bond among AHB ace and slave by recommends that of microcontroller. Controller gathering is expected upheld thought of limited state machine.

John Carter et al., [2] arranged new plan for actualizing fast memory controller abuse changed transport outline. Motivation is selective type of memory subject thinking of that has 2 assortments for old memory controlling. motivation ropes application –precise redress. Second, bolsters pre-getting at data controller in this way disguise in abundance of latency of DRAM inductions. This paper appears however motivation configuration enhances execution of memory beyond any doubt programs. It indicates change of framework execution by sixty-seven. the blend of 2 alternatives races the framework execution.

IRIET Volume: 04 Issue: 08 | Aug -2017

www.irjet.net

identification recipe over Spartan-3E FPGA stage. For constant application edge recognition equation must be finished over equipment stage. Sobel recipe is best coordinated for ongoing applications over its stylish Prewitt equation, because of its energy and space limits.

e-ISSN: 2395-0056

p-ISSN: 2395-0072

#### Shilpa and Arati [3] arranged improved testing method of AMBA memory controller with the help of example generator and rationale instrument, amid this paper a memory controller is planned with AMBA-AHB transport outline. get to time is developed with development in processor innovation. Here the framework execution is enhanced by embeddings zero crevice states once outer PC memory and compose activities with zero statuses to fringe This paper conjointly proposes correspondence that progressively makes the information exchange operations speedier looked at thereto of serial correspondence. It conjointly intends to upgrade control. the most agent recurrence of the plan is 355.77MHz. conjointly it utilize 412 mW control that is unfathomably less.

# Mrinmoy and Hsien [4] arranged practical memory controller configuration to downsize the vitality necessities for operational tradition DRAMs. This diary exhibits a quiet, low esteem technique by proposes that of time-out counters to shield control inside Drams. This take after doesn't contain few changes in limit among memory controller and DRAM, making it exceptionally suitable. All else equipment drives in memory controller that controls and issues needs invigorate operations. This strategy be quiet up to twenty 6th and on a mean twelve.12% of vitality utilized in DRAMs.

Nithin and Anjali [5] arranged a fresh out of the plastic new equipment outline for AMBA memory controller. amid this case they utilized ABH transport to interface the memory with prepare parts. Exhibitions of microchips have increased rapidly finished years. however memory dormancies and data transfer capacities have overhauled appallingly slight. As a result memory induction has been a bottleneck. in order to handle this downside, memory controllers are outlined. amid this paper a memory controller was planned abuse AMBA outline. This memory coordinator was thought of for framework memory controller with primary memory comprising of PC memory and SRAM. style given amid this paper is unbelievably clear and also demonstrates that by abuse AMBA-AHB intensity of memory controller might be intensified.

Mahamuni and Patil [6] depicts usage of foundation subtraction recipe on FPGA is clarified. Result noninheritable from foundation subtraction recipe might be another picture that holds expected information and qualities of info picture. subtracted picture contains bigger information concerning object exclusively that is in bleeding edge display.

Suthan et al., [7] presents fundamental arrangement however picture process might be depleted model basically based strategy. Some picture procedure applications is furthermore demonstrated that is done underneath SIMULINK and is upheld abuse Xilinx framework generator. This paper furthermore sets up however picture output and upgrade of picture like dim scale picture. Swapnil and Prashant [8] actualizes sobel and prewitt edge

#### 2.BASIC AMBA ARCHITECTURE

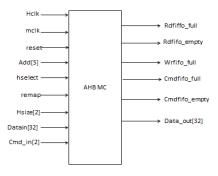

Fig 2.1:- Input and outputs of AHB

AHB methodology is blasted grounded. All operation has address and a control figure on address station. It characterizes kind of information to be moved. it is various ace and slave grounded plan. Absolutely a transport ace gives address and control markers exhibiting exchanges asked for to perform.

1.AHB ace: Bus ace begins read and compose activities. it likewise gives address and control operations. Despite the fact that it underpins different experts just a single ace will be dynamic at one time.

2.AHB slave: A transport slave answers to peruse and compose errands started by ace inside an address space arrangement. it reacts back to ace about the status of information exchange.

3.AHB information transports: Separate read compose transports are executed with the goal that tri-state drivers are not required. Most reduced information transport width is 32 bits.

HWDATA [31:0] It is compose information transport. Amid compose exchanges compose information transport is resolved by means of transport aces. All distributions are adjusted to address limit which will be equivalent to size of exchange .if exchanges are smaller than transport width measure ,slave will be in charge of choosing compose information. For burst transmission, whose transmission measure is less than width of information transport will have unique vigorous transport paths. HRDATA [31-0] it is read exchanges suitable slaves will drive the read information transports.

AHB authority: It ensures that exclusive single ace is allowed to begin information exchange at a time.AHB has

just a single mediator. It likewise acknowledges needs from slaves that craving to finish SPLIT migrations. Mediator controls which ace has induction to transport. It utilizes the positioning course of action to choose which ace has most extreme significance. Each transport ace has REQUEST/GRANT crossing point to interface with judge.

Volume: 04 Issue: 08 | Aug -2017

AHB decoder: Decoder is created to translate address of all transmission. It likewise conveys signals for slaves that are included in transmission. It performs concentrated address unraveling capacity. It enhances fringe movability. It makes the peripherals free of framework memory delineate.

#### 2.1AMBA- AHB operation

At first the transport ace must be conceded access before initiation of any exchange. Ace proclaims a welcome flag to judge which determines when ace will be permitted use of transport. After ace gets get to it begins handover by driving location and control signals. These signs give confirm on address, size of transmission. A compose information transport changes information from ace to slave and read information transport sections information from slave to ace. Information can be drawn out utilizing HREADY flag. While this flag is low it causes hold up states.

- Fundamental stream of transport activity

- Arbiter represents which ace has dish to transport

- Master begins exchange of transport

- Decoder utilizes high charge deliver lines to pick transport slaves

- Slaves offer exchange reply back to ace and information is moved among ace slave.

#### 2.2Transfer types

Transfer of information can be categorized to four types as shown below

| HTRANS[1:0] | TYPE   | DESCRIPTION                                                                                          |  |

|-------------|--------|------------------------------------------------------------------------------------------------------|--|

| 00          | IDLE   | Specifies no transmission is mandatory                                                               |  |

| 01          | BUSY   | This demonstrates is right now doing a burst exchange                                                |  |

| 10          | NONSEQ | It demonstrates<br>single exchange/first<br>exchange of a burst                                      |  |

| 11          | SEQ    | All the rest of the exchange will be consecutive. The deliver will be identified with past exchange. |  |

Table -2.1: AHB Transfer types

#### 2.2Pipelining in AMBA:

Fundamental thought of pipelining is to disintegrate direction execution system into a gathering of littler capacities that can be freely proficient by discrete subsystems in processor business. Speed relies upon different components. One conceivable strategy is to organize equipment such a route, to the point that more than one capacity should be possible at the same time. In this way number of operations done every second is all the more despite the fact that time is same. Additionally in a PC it has two separate parts one for one for bringing and other for executing them. Directions got is put away in support B1 and executed while the bring unit will be getting other guideline

#### 2.3AHB Memory Controller

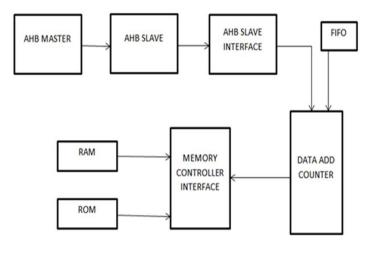

AHB memory controller can issue requests to memory. It carries on precisely like requests issued by CPU. In this venture CPU sends picture over memory controller. Slave reacts to ask for sent by ace Increase in Memory get to time limits framework execution. A memory controller is planned to take care of this issue. it controls memory. Important signs will be created with the goal that perusing and composing of confirmation from and to memory can be accomplished. It additionally assumes a noteworthy part in interfacing memory with other key parts of framework. Memory controller oversees information going into the memory and moving out of the memory .it can be put on a chip to decrease memory dormancy. in doing as such it can enhance the execution of the framework. A progressed microcontroller transport engineering as per a memory controller normally alluded to as AHB-MC is intended to control the memory. An AHBMC has three units AHB slave interface, design edge, outside memory interface. AHB-MC gives shared information way between different information way which will diminish stick number.

Fig 2.2:- Memory controller block diagram

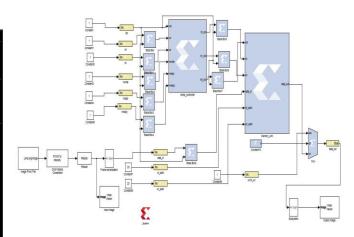

# 3. PROPOSED AMBA BASED MEMORY CONTROLLER ARCHITECTURE

Over past few years, there have been several techniques fully grown in field of dates transfer. AMBA being associate open commonplace its most typically used. however all techniques used until date uses wait statements for capital punishment scan and write operations. However within the projected system no wait states are inserted. once wait states don't seem to be occur the delay are reduced drastically. this can increase the performance of system. Here the amount of states concerned is a smaller amount as this method uses finite state machine to style memory controller. However in existing system states are relatively high. Existing system doesn't involve pipeline transfer. However during this system it involves pipeline transfer of information's that once more can raise accumulated performance system. Sometimes altogether systems information are being transferred here image are transferred.

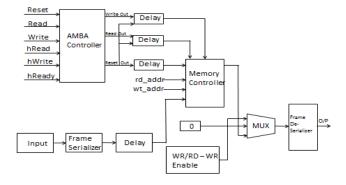

#### AMBA controller

It is standard for on-chip interchanges. It's utilized in concocting microcontrollers with remarkable show. AHB is contemporary variant of AMBA transport. it's utilized in applications wherever elite is required. Its major work is to meet prerequisites of prevalent styles. AMBA controller has choices important for prime clock.

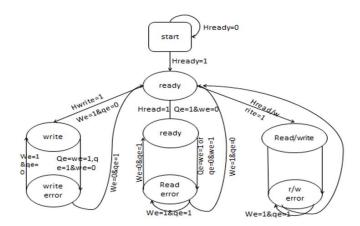

#### Memory controller

At the point when a memory controller is coordinated to a microchip, it lessens memory inertness also it will build the framework execution. Here memory controller is expected abuse limited state machine (FSM) stomach muscle initio once the flag Hready is low, framework stays in start state itself. Once the Hready goes high the framework is set up to move to progressive state. Here "H" show that the memory controller utilizes propelled superior transport plan. Once the memory controller achieves arranged state, at that point it holds up that flag it gets.

**Fig 2.3:-** System block diagram of proposed AMBA architecture

On the off chance that compose flag is gotten, that is Hwrite is high at that point compose operation is finished. Else if peruse flag is high, that is Hread is high at that point peruse operation is finished. aside from these 2 cases if peruse and compose operations must be performed while is if hread/compose flag is high, at that point the framework performs peruse compose operation. of these states also contains blunder conditions. consider A case. On the off chance that the framework Is underneath peruse condition .that is it's perusing some data from the memory. By then if compose flag goes high then it'll cause a botch condition. what's more, hence the framework can move to record mistake progress toward becoming at that occasion the controller should exclusively perform peruse operation. Once compose state is low the controller will continue peruse operation else the controller can move to arranged state.

e-ISSN: 2395-0056

**Fig 2.4**: Finite state diagram of memory controller

#### ❖ ADVANTAGES

- i. Easy engineering for plan.

- ii. We can undoubtedly add new piece to the engineering without earlier plan changes.

- iii. It can permit interface between different gadgets working at various frequencies.

#### DISADVANTAGES

- i. The transport engineering incorporates additional equipment in the plan which understudy increment zone prerequisites.

- ii. Due to the employments of high sum memory component for bigger casing, the recurrence will diminished.

- iii. Transaction of information between numerous gadget utilizing same transport is impractical.

#### **❖** APPLICATIONS

- i. Image transmitting

- ii. Image/video synchronization of advanced circuits

- iii. Communication between processors.

#### 4. BASICS OF SYSTEM GENERATOR

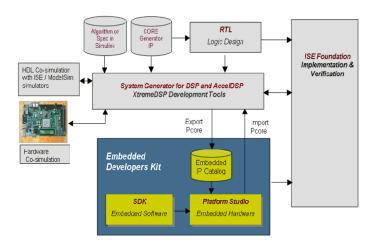

Framework generator is instrument made from Xilinx that empower use of Simulink outline condition for FPGA design. Plans are caught as square set in Simulink demonstrating condition .all FPGA execution steps are performed without human mediation to deliver FPGA programming documents. More than 80 DSP squares are conveyed in Xilinx DSP piece set for Simulink, for example, registers, multipliers, adders. It additionally offers mix stage for outline of FPGA that permit RTL, simulink parts to come composed in single reenactment and business condition. Framework generator additionally keeps up a discovery which grants RTL to be brought into Simulink and co-reenacted modelsim or Xilinx or ISE mimic. Framework generator work inside simulink grounded methodology state of mind. It makes an executable spec utilizing Simulink square sets. When usefulness and stream is computed, framework generators are utilized to illuminate equipment execution subtle elements for Xilinx gadgets. Framework generator coexist with Simulink show made plan work on utilizing standard Simulink square sets executable spec is made.

Fig 4.1: System generator flow design

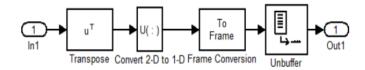

At the point when picture pre-preparing is finished utilizing matlab, it conveys contributions to FPGA as vectors which is fitting for bit stream assembling by framework generator. Following capacities are accomplished for picture handling

#### Pre-processing procedure:

- Resize: Groups input measurements for picture and introduction. it moderates fine subtle elements of picture.

- Convert 2-D to 1-D: Converts picture to lone scope of pixels

- Border modification and cradle: it sets test mode and defending information

e-ISSN: 2395-0056

Fig 4.2:Image processing

#### **Post-processing procedure:**

- Data shape modification: it modifies picture to anonymous whole number setup.

- Buffer: changes scalar representations to outline yield. Its done at low examining level.

- 1D to 2D converter: it changes 1 dimensional picture to 2 measurement picture grid

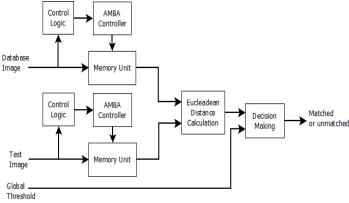

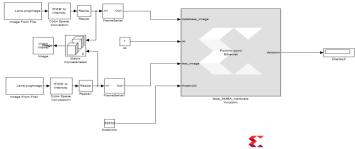

#### 5. FACE DETECTION USING AMBA ARCHITECTURE

We utilize the proposed AMBA design for confront identification application which is a live picture spilling application. The square graph of face discovery utilizing adjusted AMBA is appeared in Fig. 5.1. For this situation the database picture and test pictures are perused and store at the same time through memory utilizing AMBA controller to synchronize the camera recurrence with processor recurrence. Presently the Euclidian Distance [9] is figured by utilizing both picture pixel esteems and utilized by choice unit with edge to choose the face is coordinated or not coordinated.

Fig 5.1: Face Detection using AMBA controller

#### 6. FPGA IMPLEMENTATION

For this implementation we use ATLYS FPGA Board (xc6slx45-2csg324).

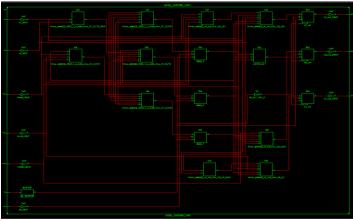

**Innovation Schematic**

The expounded perspective of the best level RTL schematic of the proposed memory controller utilizing AMBA idea is appeared in the Fig 7.3. This schematic will demonstrates the

Volume: 04 Issue: 08 | Aug -2017

www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

inner structure of the controller utilizing LUTs and flip-flops. Since FPGA will maps any rationale regarding those parts.

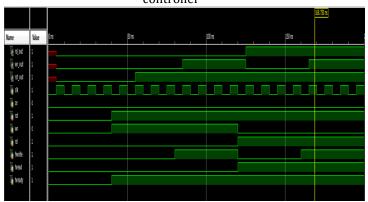

#### simulation Waveform at read-write compose cycle

The reenactment waveform of the proposed memory controller utilizing AMBA idea is appeared in the Fig 9 for both read-compose cycle at a solitary clock beat.

**Fig 6.1**: Elaborated technology schematic of AMBA controller

**Fig 6.2**: simulation Waveform at read- write compose cycle

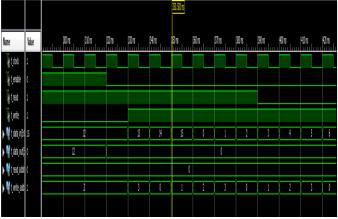

The reenactment waveform of the proposed arbitrary get to memory is appeared in the Fig 10 for both read-compose cycle at a solitary clock beat.

Fig 6.3 : Simulation result of simultaneous read-write operation

#### **Face Detection utilizing Modified AMBA Architecture**

The simulink demonstrate (programming) for confront identification utilizing proposeed AMBA engineering used to exchange a picture is appeared in Fig 11. Here the framework is set to work synchronous read-compose operation.

Fig 6.4: Simulink software for image transfer

**Fig 6.5:**Simulink hardware model for face detection using AMBA

#### **RESULT**

| Parameters                    | Shilpa and<br>Arati [3] | Vipin and<br>Nikhil<br>[11] | Proposed |

|-------------------------------|-------------------------|-----------------------------|----------|

| No. of Slice<br>Register      | 2141                    | 2784                        | 1311     |

| No. of Slice<br>LUTs          | 2377                    | 1527                        | 1613     |

| No. of<br>Occupies<br>Slices  |                         |                             | 670      |

| No. of MUXCYs                 |                         |                             | 324      |

| No. of LUT-FF pairs           | 2409                    |                             | 1889     |

| Maximum<br>Frequency<br>(MHz) |                         | 200                         | 400.09   |

Table 6.2 : Comparisons with existing techniques.

Volume: 04 Issue: 08 | Aug -2017 www.irjet.net

e-ISSN: 2395-0056 p-ISSN: 2395-0072

#### 7. CONCLUSIONS

Memory controller abuse AMBA convention for picture exchange applications has been created. We tend to utilize AMBA essentially based controller and memory interface was planned abuse state machine. Arranged plan has meeker style and adaptable setup. As framework consolidates pipelined outline general speed is raised that will build power of framework. It will expand the execution of framework by diminishing postponement and moreover this strategy will build speed and space utilization. This game plan moreover diminishes get to time.

This technique finds various applications in video prepare. Where huge information should be exchanged this methodology might be utilized. This strategy will downsize information blockage. It might be authorized in immense learning investigation. In keeping money division extraordinary measure of data should be passed. By and by affirmation and bundle exchange is finished. It might be supplanted by this system. Learning might be exchanged with none blockage.

#### **REFERENCES**

- [1] Shashisekhar Ramagundam, Sunil R. Das, Scott Morton, Satyendra N. Biswas, Voicu Groza, Mansour H. Assaf, Emil M. Petriu "Design and Implementation of High-Performance Master/Slave Memory Controller with Microcontroller Bus Architecture" Instrumentation and measurement technology (12MTC) proceedings, 2014, IEEE International.

- [2] John Carter; Wilson Hsieh, Leigh Stoller, Mark Swanson, Lixin Zhang, Erik Brunvand, Al Davis, Chen Chi Kuo, Ravindra Kuramkote, Michael Parker, Lambert Schaelicke, Terry Tateyama "Impulse: Building a Smarter Memory Controller" IEEE High-Performance Computer Architecture Symposium Proceedings, 1999

- [3] Shilpa Rao, Arati.S.Phadke "Testing of AMBA Compliant Memory Controller using Pattern Generator/ Logic Analyser" International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 2, Issue 6, June 2013

- [4] Mrinmoy Ghosh, Hsien-Hsin S. Lee "Smart Refresh: An Enhanced Memory Controller Design for Reducing Energy in Conventional and 3D Die-Stacked DRAMs" Proceedings of the 40th Annual IEEE/ACM International Symposium on Microarchitecture Pages 134-145

- [5] Nithin Joe ,Anjali Brite "A novel design approach to an amba ahb compliant memory controller" International Journal of Advances in Engineering & Technology, Nov. 2013

- [6] P.D. Mahamuni, R. P. Patil "FPGA Implementation of Background Subtraction Algorithm for Image Processing" IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE), Volume 9, Issue 5 Ver. II

- [7] A.C.Suthar, Mohammed Vayada, C.B.Patel, G.R.Kulkarni "Hardware Software co-simulation for Image Processing Applications" IJCSI International Journal of Computer Science Issues, Vol. 9, Issue 2, No 2, March 2012

- [8] Swapnil G. Kavitkar,Prashant L. Paikrao "FPGA based Image Feature Extraction Using Xilinx System Generator"International Journal of Computer Science and Information Technologies, (IJCSIT),Vol. 5 (3).

- [9] Vipin Kumar Yadav and Nikhil Kumar Sharma, "Implementation of AMBA-ASB Memory Controller with Power Analysis", IJRITCC, Vol. 3, Issue. 3, pp. 1428-1431.