# RTL Modeling for the Cipher Block Chaining Mode (CBE) for data Security

## Banumathi.T<sup>1</sup>, Abirami.G<sup>2</sup>, Renuka.G<sup>3</sup> & Deepika.M<sup>4</sup>

<sup>1,2</sup>Assistant Professor, ECE, Prince Shri Venkateshwara Padmavathy Engg College. Tamil Nadu, India. <sup>3</sup>Assistant Professor, ECE,Prince Prince Dr.K.Vasudevan College Of Engineering and Technology. Tamil Nadu, India. <sup>4</sup>Assistant Professor ,ECE, Prince Shri Venkateshwara Padmavathy Engg College. Tamil Nadu, India.

\*\*\*\_\_\_\_\_

**Abstract** - The demand of satellite communication, the security algorithms are to be designed in the board. The information from the satellite to the ground is required the data security with the cryptographic algorithms. Advanced encryption standard (AES) is one of the promising cryptographic algorithms for the terrestrial communication. In this paper, the encryption and decryption is mainly focused on the cipher block chaining (CBC) mode for achieving the high secured data transmission. For efficient data transmission, the AES algorithm is implemented by using CBC mode. The proposed work is designed by using RTL modeling and also the minimum numbers of logical elements are used for implementation.

*Key Words*: Advanced Encryption Standard, Cipher block chaining, data security, Register transfer level, Data transmission.

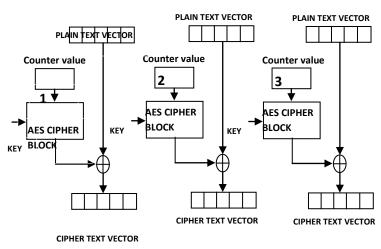

### **1. REVIEW OFCIPHER BLOCK CHAINING MODES**

The design is capable of maintaining throughput during key changes given a maximum of one change every 120 cycles. The another design has a throughput of 28.5 Gbps and supports key changes every cycle. The floor planning and a pipelined key expander were developed together with modifications to the mix columns and composite field implementation of Sub Bytes operation. AES secure channel of any feedback mode including cipher block chaining. Christy M A et al., [3] described the security data transmission algorithm in cryptography is advanced encryption algorithm. The pass transistor logic is used for the minimal power consumption and achieves the less number of transistor counts. Using a simple exclusive OR gate that is XOR gate pass transistor logic is used to minimize the power. The power consumption of mix column is reduced in AES. XOR gates are constructed by using six pass transistors which reduce the number of large transistor counts. Yousef S et al., [5] described the stream cipher algorithm based on modified AES block cipher concept to achieve high complexity in encryption and decryption processes. The stream cipher uses three functions, two of them are modified sub byte and one is modified mix column transformation of AES algorithm with an addition to the permutation function. Tiny blocks of sizes (2\*2, 4\*4,6\*6,...) have been implemented in the algorithm.

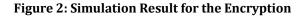

2. SIMULATION RESULTS

### L wave = default Fe fat Vew Add Famat Tools Window D-GE Let Vew Add Famat Tools Window D-GE Let Vew Add Famat Tools Window D-GE Let Vew Add Famat Tools Window Vestages Ve

© 2017, IRJET

**Impact Factor value: 5.181**

Volume: 04 Issue: 08 | Aug -2017

www.irjet.net

p-ISSN: 2395-0072

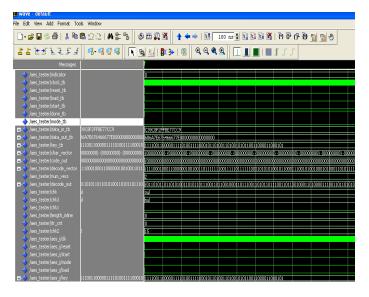

Figure 3: Simulation Result for the Decryption

### **3. SYNTHESIS RESULTS ANALYSIS**

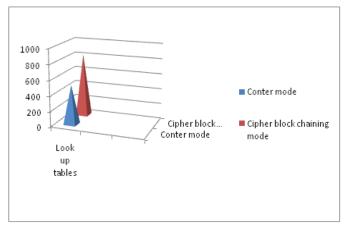

In order to achieve the high secured data transmission, the Cipher block chaining mode is to be implemented instead of the counter mode. By using counter mode is increasing the LUT counts and the power utilizations. The CBC mode is implemented in the encryption and decryption to achieve the high efficiency level in terms of VLSI design environment. The synthesis results are carried out by using the Xilinx ISE design suite.

**Chart -1**: Synthesis results for the Look-Up-Tables utilizations.

### **4. CONCLUSIONS**

The proposed Cipher block chaining (CBC) mode based encryption and decryption is improving the area utilizations compare than the traditional method. The proposed work is designed by using Verilog HDL language. The simulation is evaluated by suing the Modelsim XE and the synthesis results are generated by using the Xilinx ISE.

### REFERENCES

- [1] High Speed Low Cost Implementation Of Advanced Encryption Standard On FPGA- International Journal of Electronics & Telecommunication and Instrumentation Engineering (IJETIE), March 2010.

- [2] Scalable 128-bit AES-CM Crypto-Core Reconfigurable Implementation for Secure Communications, IEEE conferebnce on 2010.

- [3] Implementation and Performance Analysis of AES-128 CBCalgorithmin WSNs- Hyeopgeon Lee, KyounghwaLee, Yongtae ShinDepartmentof Computingt, Soongsil University, Korea.

- [4] High-Speed VLSI Architectures for the AES Algorithm -EEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 12, NO. 9, SEPTEMBER 2004.