### **Transient Protection for two terminals HVDC System**

### P V N Mohan Krishna<sup>1</sup>, A.Hemanth kumar Raju<sup>2</sup>, M.E.C.Vidya Sagar<sup>3</sup>

<sup>1,2,3</sup> Dept. of Electrical and Electronics Engineering, SRKR Engg college, A.P, India

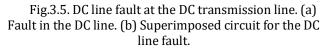

Abstract - The relation between the parameters of dc transmission line and the variation of transient energy has been analyzed under various fault conditions in this paper. According to that, a new transient energy protective scheme is proposed. It is developed based on the distributed parameter line model in which the transient energy distribution over the line can be obtained from the voltage and current measurements at both terminals and the fault can be recognized from the calculated value simply. The test system is modelled based on the CIGRE benchmark and considered the distributed parameters of the dc transmission line. Comprehensive test studies show that the performance of transient energy protection scheme is encouraging. It can not only identify internal fault and external faults correctly and quickly, but can also respond to the high ground resistance fault. Finally, two main factors, including fault resistance and transmission distance, that affect the performance of the protection are also discussed. Index Terms—HVDC, test and result, transient

*Key Words*: Transient Energy, HVDC

#### **1. INTRODUCTION**

RECENTLY. the number of high-voltage direct current(HVDC) systems is increasing rapidly throughout the world, due to their advantages of long distance and large capacity power transmission, asynchronous interconnections, and their ability to prevent inadvertent loop flows in an interconnected ac system [1]-[3]. These definite technical and environmental advantages make HVDC transmission systems more attractive than highvoltage alternating current (HVAC)systems in power system projects. Over the last two decades, HVDC transmission systems developed more rapidly than HVAC transmission systems around the world. The traditional protection system for the HVDC transmission line often uses the voltage and its change rate to detect the ground fault in the dc line [4]. But it is affected easily by fault impedance. With the rapid advance of microelectronics technology and microcomputer protections, travellingwave theory has been implemented and adopted in HVDC transmission lines successfully [5]. However, travellingwave-based methods still have problems that limit their application, such as lacking mathematical tools to represent travelling wave, being easily influenced by noise, and so on [6], [7]. Recently, based on the characteristics of low-frequency differential transient energy at the two ends of the dc line, a new protection scheme for UHVDC lines is proposed . However, this paper does not take into account the distributed parameters of the transmission line. Infact, the typical characteristic of modern HVDC transmission systems is the long distance;

thus, the effect of the distributed parameters cannot be ignored and may cause the mal operation of relay protection .A novel transient energy principle is proposed in this paper. Based on the steady-state transmission-line equations, the distributed parameters of the dc line have been taken into account. The increments of transient energy in the dc line are utilized to identify internal fault and external fault. With PSCAD/EMTDC, the test system is modelled considering the distributed parameters. Comprehensive test studies show that the proposed principle is simple, reliable, and practical. It can provide correct responses under various fault conditions including high ground resistance faults. Finally, the two main factors that affect performance of the protection are also discussed: fault resistance and transmission distance. And the relationships between the two factors and the sensitivity of transient energy protection have been deduced.

This paper is organized as follows. In Section II, the protection principle used in this paper is given. The test system is given in Section III. Test results are given in Section IV, followed by the conclusions in Section V.

1.1 TRANSIENT ENERGY PROTECTION PRINCIPLE FOR TWO TERMINAL HVDC SYSTEM.

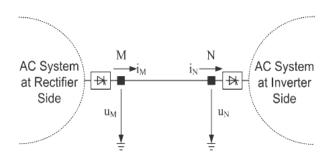

Fig -1: Diagram of the HVDC transmission system.

Before Fig.1 shows a main structure diagram of the typical HVDC transmission system. The dc transmission-line protection devices are installed at the two ends of the line M and N.  $i_M$ ,  $i_N$  and  $u_M$ ,  $u_N$  are dc currents and dc voltages at M and N, respectively. The positive directions of the aforementioned electrical vectors are defined in the diagram.

The transient energy of the measuring point from  $t_{1}$  to  $t_{2} {\rm is}$

$$E_{M} = \int_{t_{1}}^{t_{2}} p_{m}(t)dt$$

(1)

$$E_{N} = \int_{t_{1}}^{t_{2}} p_{n}(t)dt$$

The increment of the transient energy can be expressed as

$$\Delta E_M = \int_{t_1}^{t_2} \Delta p_m(t) dt$$

(2)

$$\Delta E_N = \int_{t_1}^{t_2} \Delta p_n(t) dt$$

Where  $p_m(t)$  and  $p_n(t)$  are instantaneous power of the measuring point, and  $\Delta p_m(t)$  and  $\Delta p_n(t)$  are their increments. Equation (2) can be converted to discrete form by substituting n. $\Delta t$  for the continuous period from  $t_1$  to  $t_2$ .

$$\Delta E_{M} = \sum_{i=1}^{n} \Delta p_{mi}(t) dt$$

$$\Delta E_{N} = \sum_{i=1}^{n} \Delta p_{ni}(t) dt$$

(3)

Where  $\Delta t$  the sampling interval and n is is the time index. Further the increase the increase in DC voltage and DC current is expressed as  $\Delta u_M, \Delta i_M, \Delta u_N, \Delta i_N$ . So the increment of transient energy can be obtained as follows:

$$\Delta E_{M} = \sum_{i=1}^{n} \Delta u_{mi} \Delta i_{mi} \Delta t$$

$$\Delta E_{N} = \sum_{i=1}^{n} \Delta u_{ni} \Delta i_{ni} \Delta t$$

(4)

Therefore the increase of transient energy in the dc transmission line is

$$\Delta E = \Delta E_M - \Delta E_N \tag{5}$$

In steady state operating condition

$$\Delta E_M = \Delta E_N = 0 \tag{6}$$

Begin

#### 3.2 FAULTS:

#### 3.2.1 External fault:

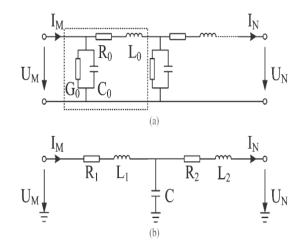

Fig 3.2 Demonstration of line models. (a) Distributed parameter model.

(b) Lumped parameter model with the shunt capacitance.

Where  $R_0$  is the series resistance  $\Omega/\text{km}$ ,  $L_0$  is the series inductance (H/km),  $G_0$  is the shunt leakage conductance (S/km).

Equations of the transmission line are

$$-\frac{\partial u}{\partial x} = Ri + L\frac{\partial i}{\partial t}$$

$$-\frac{\partial u}{\partial x} = Gu + C\frac{\partial u}{\partial t}$$

For simplicity the impact of leakage conductance is neglected. Its equivalent circuit is shown in Fig. 3.2(b). The dc line that has to be protected is replaced by a lumped parameter model considering the influence of shunt capacitance. The increase of voltage and current due to distributed parameters of the transmission line can be expressed as:

$$u_L = R_1 i_M + R_2 i_N + L_1 \frac{di_M}{dt} + L_2 \frac{di_N}{dt}$$

$$i_c = c \frac{du_c}{dt}$$

Where  $u_L = u_M - u_N$

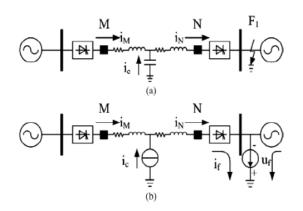

Fig. 3.3(a) shows that the series inductance of the dc transmission line is affected during external fault at the inverter side. The system impedance decreases with fault  $F_1$  and becomes smaller than normal operation. Hence the voltage at both the ends of the transmission line drops down rapidly.

Fig. 3.3(b) shows superimposed fault current  $i_f$  from that we get transient current at both ends of dc transmission line during fault  $F_1$ .

$$i_{M1} = i_M + i_f \tag{11}$$

$$i_{N1} = i_N + i_f$$

(12)

Substituting the relations of (11) and (12) in equation (8) we get

$$u_L = R_1 i_{M1} + R_2 i_{N1} + L_1 \frac{d i_{M1}}{dt} + L_2 \frac{d i_{N1}}{dt}$$

(13)

And

$$u_{M1} - u_{N1} = u_L$$

(14)

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 239

Volume: 05 Issue: 02 | Feb-2018

www.irjet.net

Fig. 3.3.External fault at the inverter side considering the series inductance of the dc transmission line. (a) Diagram of the external fault. (b) Superimposed circuit for the external fault.

Before the fault has occurred, we have

$$u_M - u_N = R_1 i_M - R_2 i_N \tag{15}$$

It means

$$\Delta u_M - \Delta u_N = (R_1 + R_2)i_f + L_1 \frac{di_{M1}}{dt} + L_2 \frac{di_{N1}}{dt}$$

(16)

Hence there are

$$\Delta u_M < 0 \text{ and } \Delta u_N < 0 \tag{17}$$

$$|\Delta u_M| < |\Delta u_N| \tag{18}$$

Shunt capacitance of the dc transmission line affects the dc protection of the dc line. Shunt capacitance between the overhead dc line and ground is present during normal operating conditions.

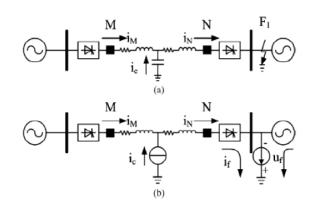

Therefore, with the fault  $F_1$  the capacitance current is discharged from the shunt capacitance. Equivalent capacitance C and the discharging current  $i_c$  are represented in Fig.3.4 (a), and an equivalent current source that is used to substitute for the discharging current under the transient state condition is shown in Fig. 3.4(b).

According to (9) the equivalent discharge current of the dc line is

$$i_c = c \frac{du_c}{dt} \tag{19}$$

Hence the transient current of the dc line during the fault  $F_1$  is obtained as,

$$i_{M1} = i_M + i_f - \frac{1}{2}i_C$$

(20)

$i_{N1} = i_N + i_f - \frac{1}{2}i_C$  (21)

Fig.3.4. External fault at the inverter side considering the shunt capacitance of the dc transmission line. (a) Diagram of the external fault. (b) Superimposed circuit for the external fault.

And the increments in the two transient currents are

$$\Delta i_M = i_f - \frac{1}{2}i_C \qquad (22)$$

$$\Delta i_M = i_f + \frac{1}{2}i_C \qquad (23)$$

Since  $i_f > i_c$  we get

$\Delta i_M > 0, \ \Delta i_N > 0 \quad (24)$

$$\Delta i_M | < |\Delta i_N| \tag{25}$$

Substituting (17), (18) and (24), (25) into (4) we get

$\Delta u_M \Delta i_M < 0 \text{ and } \Delta u_N \Delta i_N < 0$

$$|\Delta u_M \Delta i_M| < |\Delta u_N \Delta i_N|$$

Substituting these relationships into (5), we get

$\Delta E > 0.$

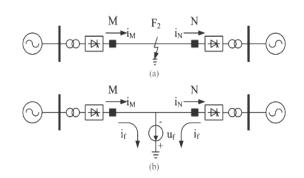

#### 3.2.2 DC line fault:

With the internal fault occurring as illustrated in Fig.3.5 (a), the voltages of at two ends of the dc line drop sharply. The superimpose circuit of the HVDC transmission system is shown in Fig. 3.5(b), where is  $u_f$  the additional fault voltage source and  $i_f$  is the additional fault current. On this condition, the current  $i_M$  always ascends while  $i_N$  descends.

So the increment of transient voltage and current can be concluded as.

$$\Delta u_M < 0$$

$$\Delta u_N < 0$$

$$\Delta i_M > 0$$

$$\Delta i_M < 0$$

$$\Delta i_M < 0$$

Substituting these relationships into (4), we have

$$\Delta E_M < 0$$

$$\Delta E_N > 0$$

(27)

Substituting these relationships into (5), we have

#### 3.4 RESULTS:

#### **Test for Various Faults:**

| Fault type         | ∆Em/Kw.ms | ∆En/Kw.ms | ∆E/Kw.ms | operation |

|--------------------|-----------|-----------|----------|-----------|

| Rectifier<br>fault | 2.9954    | 2.0152    | 0.9803   | -         |

| Inverter<br>fault  | 1.240     | 0.7559    | 0.4841   | -         |

| Internal<br>fault  | -0.3553   | 0.9684    | -1.3237  | +         |

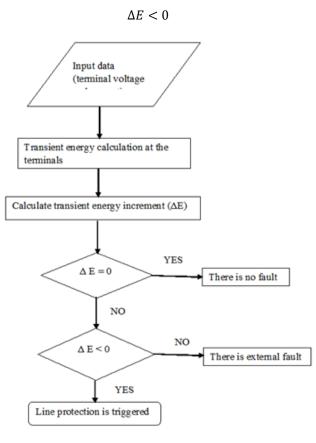

#### **3.4.1 Results for the DC Line Fault:**

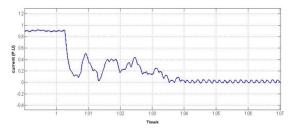

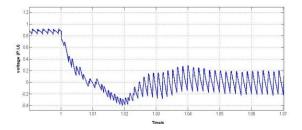

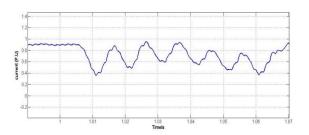

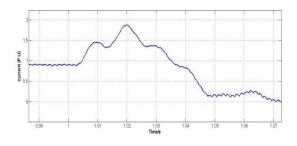

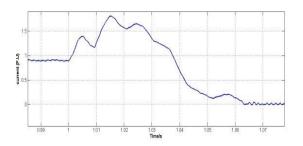

A fault occurred on the dc line at 1.0sec. Fig.3.7 shows the four response curves. Obviously, the two dc voltages and will drop immediately as soon as the dc fault occurs. The dc current drops and soars rapidly. Therefore, the

increment of transient energy at the rectifier is negative, and the one at the inverter is positive. There is the transient energy difference between two terminals of the dc transmission line. And the value is negative, so the internal fault is detected easily by the new scheme.

(a) Current response during the dc-line fault at rectifier side

(b) Current response during the dc-line fault at inverter side

(c) Voltage response during the dc-line fault at rectifier side

(d) Voltage response during the dc-line fault at inverter side

Fig.3.7. System response during the dc-line fault.

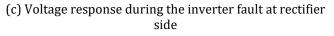

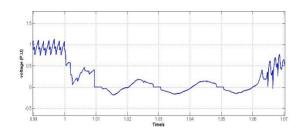

# **3.4.2 Results for the Balanced Fault at the Rectifier Side:**

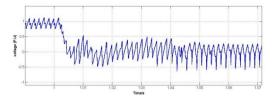

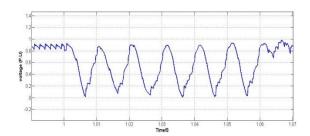

A fault occurred at the rectifier side at 1.0sec. Fig.3.8 shows the response curves during that fault. When the ac system fault occurs at the rectifier side, the two dc voltages and will descend immediately, and the dc

currents will decline. In addition, due to the influence of the equivalent shunt capacitor in the dc line, the current is smaller than during the transient process. The voltage decreases slower than considering the influence of the equivalent series inductance at that time. So there is the transient energy difference between two terminals of the dc transmission line. And the value is positive; thus, the external fault is recognized by the new scheme.

(a) Current response during the rectifier fault at rectifier side

(b) Current response during the rectifier fault at inverter side

(c) Voltage response during the rectifier fault at rectifier side

(d) Voltage response during the rectifier fault at inverter side

Fig.3.8. System response during the rectifier fault

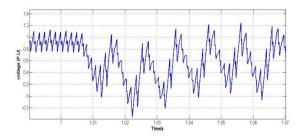

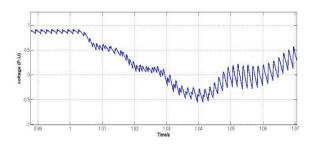

# **3.4.3 Results for the Balanced Fault at the Inverter Side:**

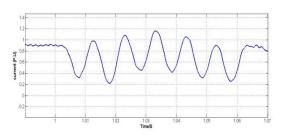

A fault occurred at the inverter at 1.0sec as shown in fig.3.9 four curves of system responses during the ac system balanced fault at the inverter side dc current and dc voltage in the dc line close to the rectifier, dc current and dc voltage in the dc line near the inverter. When the ac system fault occurs at the inverter side, the dc voltage slump, on the contrary, the dc current increase speedily. At that time, constant current (CC) and constant extinction angle (CEA) work and attempt to stabilize the dc system. However, the big disturbance of the ac system makes dc current increase greatly. In addition, due to the influence of the equivalent shunt capacitor in the dc line, the dc current on rectifier side is lower than current on inverter side during that transient process. It is clear that the voltage on rectifier side is higher than on inverter side at that time. Therefore, there is a transient energy difference between two terminals of the dc transmission line. And the value is positive, so the external fault can be detected by the new scheme.

(a) Current response during the inverter fault at rectifier side

(b) Current response during the inverter fault at inverter side

(d) Voltage response during the inverter fault at rectifier side

Fig.3.9. System response during the inverter fault

#### CONCLUSIONS

- A transient energy scheme for multi terminal HVDC transmission system is proposed.

- The relation between the parameters of the dc transmission line and protection has been deduced.

- Based on the test system, the different operation conditions and various faults are tested.

- For two terminal HVDC system external fault and internal fault has been identified using transient energy scheme.

- For multi terminal HVDC system also the fault location has been identified using this transient energy scheme.

- Test studies show that the performance of transient energy scheme is satisfied.

#### REFERENCES

- [1] P. F. Gale, P. V. Taylor, P. Naidoo, C. Hitchin, and D. Clowes, "Travelling wave fault locator experience on Eskom's transmission network," in Proc. 7th Int. Conf. Develop. Power Syst. Protect., 2001, vol. 4, no. 479, pp. 327–330.

- [2] X. L. Liu, A. H. Osman, and O. P. Malik, "Hybrid traveling wave/ boundary protection for monopolar HVDC line," IEEE Trans. Power Del., vol. 24, no. 2, pp. 569–578, Apr. 2009.

- [3] G. WANG, J. B. LUO, H. F. LI, and Z. K LI, "Transient energy protection for 800 kv uhvdc transmission lines," (in chinese) Autom. Elect. Power Syst., vol. 34, no. 1, pp. 28–31, Jan. 2010.

- [4] K. K. Li, C. Fan, W. L. Chan, and W. Y. Yu, "Study of protection scheme for transmission line based on wavelet transient energy," Int. J. Elect. Power Energy Syst., vol. 28, pp. 459–470, Feb. 2006.

- [5] Xiaodong Zheng, Tai Nengling, Yang Guangliang, and Ding Haoyin "A Transient Protection Scheme for HVDC Transmission Line," IEEE transactions on power delivery, vol. 27, no. 2, april 2012

- [6] M. Szechtman, T. Wess, and C. V. Thio, "First benchmark model for HVDC control studies," Electra, vol. 135, no. 4, pp. 54–73, April 1991.

- [7] M. O. Faruque, Y. Zhang, and V. Dinavahi, "Detailed modeling of CIGRE HVDC benchmark system using PSCAD/EMTDC and PSB/SIMULINK," IEEE Trans. Power Del., vol. 21, no. 1, pp. 378–387, Jan. 2006.