# Arithmetic logic Unit Design with Comparison Power Consumption on Different Foundries using Microwind Tool

Sonam Rathore<sup>1</sup>, Shiwani Singh<sup>2</sup>

<sup>1</sup>Assistant Professor in Department of Electronics and Communication, Shri Ram Murti Smarak Institutions, Bareilly U.P.

<sup>2</sup>Assistant Professor in Department of Electronics and Communication, Shri Ram Murti Smarak Institutions, Bareilly U.P.

\*\*\*

**Abstract -** : In this paper, An ALU design and implementing using different foundries like 50nm, 70nm, 90nm and 120nm. The performance of developed ALU analyzing and comparing in terms of area and power. The schematic of ALU circuit designing using DSCH 3.5 and its equivalent layout creating using Microwind tool.

*Keywords*: ALU, Foundries, Area, Power, DSCH, MicroWind Tool

# **1. INTRODUCTION**

In Present era, as the technology is growing more and in terms of IC design, more number of transistors getting packed into an IC, which increases the size and total area in any physical design of device. So, at present, scaling is important for designing any device. So, other than Very large scale integration, there will be a existence of Ultra large scale integration technologies, for faster operation.

Major challenge is microscopic issues as ultra-high speed power dissipation and supply rail drop growing importance of interconnect noise, crosstalk reliability, manufacturing clock distribution. Low power also leads to smaller power supplies, less exclusive batteries, and enables products to be powered by signal lines (such as fire alarm wires) lowering the cost of the end result. The arithmetic logic unit (ALU) is the core of a CPU in a computer. The adder cell is the basic unit of an ALU. The constrictions the adder has to satisfy are area, power and speed requirements.

### 2. METHODOLOGY

### 2.1. ALU Design with Power Consumption

The ALU receives the information from the registers and performs a given operation as specifies by the control. A very simple ALU design, the control unit is made up of 4-1 multiplexer. The operation part consists of four kinds follows: and, or, addition and subtraction. The 'and' and 'or' operation are realized by using the basic logic gates. The addition and subtraction are realized using the ADDER user symbols. A full adder could be defined as a combinational circuit that forms the arithmetic sum of three input bits .A digital multiplexer made from MOS device selects one of the 4 operations results and directs it to a single output line. The full adder performs the computing function of the ALU. A full

adder could be defined as a combinational circuit that forms the arithmetic sum of three key in or input bits. It consists of three inputs and two outputs. Arithmetic functions like as addition, subtraction, multiplication and division are some examples.

The design criterion of a full adder cell is usually multi-fold. Transistor count is, of course, a primary concern which largely affects the design complexity of many function units such as multiplier and algorithmic logic unit (ALU). The limited power supply capability of present battery technology has made power consumption an important figure in portable devices [2]. The power consumption in a CMOS digital circuit can be calculated using Eq.1. Whether it is a general-purpose system or an application specific processor, addition is by far the most frequently used operation.[4]

$P = f'C.Vdd^2 + f'Ioff.Vdd + Ioff.Vdd$ (1)

| ALU truth table |    |               |        |                |  |

|-----------------|----|---------------|--------|----------------|--|

| Control         |    | Select points | Result | Carry out      |  |

| F1              | F0 |               |        |                |  |

| 0               | 0  | Pass          | А      | 0              |  |

| 0               | 1  | Add           | A+b    | Carry from a+b |  |

| 1               | 0  | And           | A • b  | 0              |  |

| 1               | 1  | Not           | A'     | 0              |  |

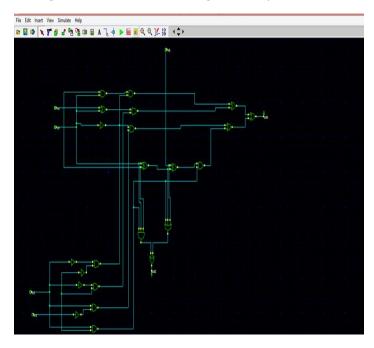

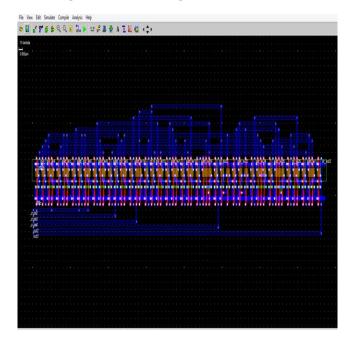

Now drawing the Schematic diagram of 1 bit ALU using DSCH-3.5 EDA tool will result in the gate level implementation of the circuit as in Figure.1 and Figure.2

### **3. SCHEMATIC AND LAYOUT**

The schematic and layout of 1 bit ALU in DSCH schematic is designed. An arithmetic logic unit, or ALU (sometimes pronounced "Al Loo"), is a combinational network that implements a function of its inputs based on either logic or arithmetic functions. ALUs are at the heart of all computers as well as most digital hardware systems. The arithmetic and logic unit (ALU) performs all arithmetic operations (addition, subtraction, multiplication, and division) and logic

maneuvers. Logic operations test various conditions encountered during processing and allow for different actions to be taken based on the results. The data required to perform the arithmetic and logical functions are inputs from the designated CPU registers and operands. The ALU relies on fundamental items to perform its operations.

The schematic design using different symbols from libraries and connect it.Making Verilog File and save it. Then compile Verilog file in Microwind tool and generate layout.

Fig 1. Schematic Diagram of 1 Bit ALU

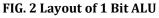

# 4. SIMULATION AND RESULTS

Fig. 3 Simulation of 1 bit ALU in 50 nm

Fig. 4. Simulation of 1 bit ALU in 70 nm

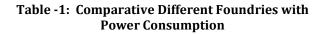

| Different Foundries | Power<br>Dissipation |

|---------------------|----------------------|

| 50 nm               | 8.716µW              |

| 70nm                | 68.516µW             |

| 90nm                | 62.19µW              |

| 120nm               | 97.466µW             |

Fig. 4 . Simulation of 1 bit ALU in 90 nm

International Research Journal of Engineering and Technology (IRJET)e-ISSN: 2395-0056Volume: 06 Issue: 12 | Dec 2019www.irjet.netp-ISSN: 2395-0072

Fig. 5 Simulation of 1 bit ALU in 120 nm

### **5. CONCLUSIONS**

The schematic design using different symbols from libraries and connect it. Making Verilog File and save it. Then compile Verilog file in Microwind tool and generate layout and simulate in different foundries.

The comparison of different power dissipation as shown in table 1. A comparative study of the silicon area and the power consumption has been done in the circuit using different channel lengths such as 50nm, 70nm, 90nm and 120nm. The circuit is designed and simulated using DSCH schematic tool and the layout is developed by Microwind VLSI CAD Tool. The designed circuit has shown a remarkable reduction in the consumed power of 90% in 50nm foundry as compared to 120 nm foundry

#### REFERENCES

[1]. Anu, Shilpa Goyal; Department of Electronics Engineering, YMCA University, Faridabad, Haryana; "A Literature Review on Leakage and Power Reduction Techniques in CMOS VLSI Design", International Journal on Recent and Innovation Trends in Computing and Communication, ISSN: 2321-8169, Volume:3 Issue:

[2]. Kunal & Nidhi Kedia ; Dhenkanal, Odisha; "GDI Technique : A Power-Efficient Method for Digital Circuits"., ISSN (Print): 2278-8948, Volume-1, Issue-3, 2012.

[3]. T. Esther Rani, M. Asha Rani and Dr. Rameshwar rao, "Area optimized Low-power Arithmetic logic unit", 978-1-4244-8679-3/11/2011 IEEE.

[4]. K. Chang, S. Huang, "The novel efficient design of XOR/XNOR function for full adder applications", IEEE international conference on Electronics. Circuits and Systems, 1999.

[5]. Singh, Jyoti Budakoti, India, "Energy Efficient Advanced Low Power CMOS Design to reduce power consumption in Submicron Technologies in CMOS Circuit for VLSI Design", Int. Journal of Advanced Research in Computer Communication Engineering, Vol. 3, Issue 6, June 2014. [6]. Kunal & Nidhi Kedia ; Dhenkanal, Odisha; "GDI Technique : "A Power-Efficient Method for Digital Circuits"., ISSN (Print): 2278-8948, Volume-1, Issue-3, 2012.

[7]. Bagadi Madhavi, G Kanchana, India., "Low Power and area efficient design of VLSI Circuits", International Journal of Scientific and Research Publications, April 2013, Volume 3, Issue 4, April 2013, ISSN 2250-3153.

[8] W. Wolf, Modern VLSI Design- Systems On Silicon, Prentice Hall, 1998 2) Y. Tsividis, Operation and Modeling of The MOS Transistor, Mc Graw-Hill, 1999. [9] J.M. Rabaey, Digital Integrated Circuits- A Design Perspective, Prentice Hall, 1996. 4) M. Morris Mano, Digital Logic and Computer Design, Prentice Hall, 1979. [10] P. Chandrakasan, S.Sheng, and R.W.Broderson, "Low-power CMOS digital design," IEEE J. Solid-State Circuits, vol. 27, pp. 473–483, Apr. 1992

# BIOGRAPHIES

SONAM RATHORE Mtech(VLSI DESIGN) B.E.(Electronics& Instrumentation) Assistant Professor Department of Electronics and Communication Shri Ram Murti Smarak Institutions, Bareilly U.P.