# **Review on Dynamic Reconfiguration of Filters for Signal Processing**

Ms. Chaitali Suroshe, Dr. N.K. Choudhari

<sup>1</sup>PG Student, M.Tech, Department of Electronics &Communication Engineering, Priyadarshini Bagwati College of Engineering <sup>2</sup>Professor, Department of Electronics & Communication Engineering, Priyadarshini Bagwati College of Engineering

\*\*\*\_\_\_\_\_

**Abstract:** In this paper we describe a dynamically reconfigurable photo processing machine that reaches actual time video processing performances notwithstanding reconfiguration time overhead. The system is composed of reconfigurable pixel processing units set to technique several pixels in parallel. We gift a scheme for optimizing a LUT-based architecture by means of without delay mapping it into the Xilinx FPGA CLB primitives. Internally controlled Dynamic Partial Reconfiguration is to regulate the LUT values at runtime with out stalling the overall operation. The mixture of optimized implementations with CLB primitives and Dynamic Partial Reconfiguration results in multifunctional, area-efficient, and high-overall performance realizations of LUT-based pixel processing structures.

Reconfigurable gadgets, along with contemporary FPGA provide superior capabilities which permit the introduction of embedded structures on single chips (SoC). One of the maximum hard opportunities supplied with the aid of this sort of gadgets is the capability to dynamically and partially reconfigure them. It is composed within the modification of a part of the circuitry mapped on the FPGA at the same time as the machine is going for walks. This capacity lets in development of flexible structures which could cope with modifications within the requirements, requirements and operational conditions. This paper provides in part reconfigurable FIR clear out design that employs dynamic partial reconfiguration. Our scope is to put in force a lowelectricity, location-green autonomously reconfigurable digital signal processing architecture this is tailor-made for the realization of many response FIR filters the use of Xilinx FPGA. The implementation of layout addresses area efficiency and flexibility permitting dynamically inserting and/or putting off the partial modules to enforce the partial reconfigurable FIR filters with diverse sorts.

# Keywords: FIR, FPGA, SoC, LUT

# **1. INTRODUCTION**

General-reason image filters lacks the power and adaptableness for un-modeled noise types. The reconfiguration circuit based picture filtering algorithm is considered as a method to beautify overall performance with out compromising photograph visual pleasant. The hardware aid requirements may be altered in reaction to noise situations for a set MDPP. A widespread quantity of noise demands a massive number of repeated reconfigurations, to acquire a MDPP similar to that carried out for a much less noisy photograph. In this work, in

imposing the VRC primarily based image filter out, the dynamic reconfiguration Structure is proposed via thinking about both the reconfiguration options, highquality-timescale and coarse-timescale reconfiguration. Reconfiguration of the photograph filter is accomplished in accordance to versions in noise conditions over seconds. Reconfiguration at the moment scale minimizes the overall performance impact of millisecond FPGA reconfiguration instances. Coarse-timescale reconfiguration is encouraged by way of converting noise traits from parameters such as climate, distance, or digicam battery power. These parameters result in a signal-tonoise ratio (SNR) that adjustments incredibly sluggish. When extra advanced photograph nice is needed, a lower clock-speed can be used. When less accuracy is needed, a better-performance circuit is swapped in. If dynamic reconfiguration was no longer allowed, the lower-overall performance circuit could usually need to resident. Current FPGA architectures require be reconfiguration times measuring in milliseconds. FIR filters are employed in the general public virtual signal processing (DSP) based totally electronic systems. The emergence of disturbing packages (image, audio/ video processing and coding, sensor filtering, etc.) in phrases of velocity, overall performance, electricity, device compatibility and reusability make it imperative to layout the reconfigurable architectures. This paper provides a partially reconfigurable FIR filter design that targets to satisfy all the targets (low-electricity intake, autonomous adaptability/reconfigurability, fault-tolerance, and so on.) on the FPGA. FPGAs are programmable logic devices that allow the implementation of virtual systems. They offer an array of common sense cells that may be configured to perform a given functionality through a configuration bitstream. (DSP) based digital structures. The emergence annoving packages (software defined of radio, image, audio/video processing and coding, sensor filtering, and many others.) in phrases of power, velocity, overall performance, machine compatibility and reusability make it vital to layout the reconfigurable architectures. Moreover, in case of aerospace application, there is the added difficulty for fault-tolerant FIR filtering fabrics, that are succesful to respond to diverse malfunctions prompted through endogenous or exogenous elements.

This paper offers a partially reconfigurable FIR clear out layout that goals to satisfy all the targets (low-strength consumption, self sufficient adaptability/reconfiguration potential, fault-tolerance, and so on) on the Xilinx Virtex-4

## FPGAs.

The FPGAs are programmable logic gadgets that allow the implementation of digital systems. They provide an array of good judgment cells which can be configured to perform a given capability by way of a configuration bit-stream. Many of FPGA systems can handiest be statically configured. Static reconfiguration means to configure the tool completely earlier than gadget execution. If a brand new reconfiguration is needed, it's far necessary to forestall the machine execution after which reconfigure the tool it once more. Some FPGAs allow acting partial reconfiguration, wherein a reduced bit-move reconfigures best a given subset of internal components. Dynamic Partial Reconfiguration (DPR) permits the part of FPGA tool be modified at the same time as the relaxation of the tool (or device) continues to perform and unaffected by means of the reprogramming [

# 2. The Proposed Work

The proposed system comprises five different modules that are as follows:

- 1. Dynamical reconfigurable FIR filter.

- 2. The multiprecision multiplier;

- 3. The input operands scheduler (IOS) whose task is to reorganize the input data stream into a buffer and thereby decrease the vo transitions;

- 4. The frequency scaling unit produces the necessary operating frequency of the multiplier;

- 5. The MP multiplier has razor flip-flops which can report timing errors related to unsatisfactorily high voltage supply levels.

## Slice-based Bus macro

Slice-based bus macros provide a means of locking the routing between PRMs and the base design, making the PRMs pin compatible with the base design. As a result all connections between the PRMs and the base design must pass through a bus macro, with the exception of the clock signal. Hardwired slice-based bus macro guarantees that routing channels between modules remain unchanged, avoiding contentions inside the FPGA and keeping correct inter module connection even though each time partial reconfiguration is performed. New partial reconfiguration design method provides various type of bus macro in terms of device, direction and synchronicity.

The fundamental goal is to design and enforce a minimum delay reconfigurable clear out layout that mixes MP multiplier with an error-tolerant DFS approach primarily based on razor flip-flops. This deals with the examine, design and implementation of multiprecision array multiplier with parallel processing. Architecture of fir filter out primarily based on partial reconfiguration is designed here.The FIR clear out calculates an output from a collection of input samples. The institution of input samples is elevated by way of a set of coefficients after which added together to generate the output. Realization of FIR filters can be completed in either hardware or software program .A software implementation would contain sequential execution of the filter capabilities at the same time as hardware implementation of FIR filters lets in the clear out functions to be processed in a parallel way, that enhances processing speed but less flexible for modifications. Thus, the proposed machine offers both the power of pc software and the capability to create custom excessive overall performance systems

#### **3. BLOCK DIAGRAM**

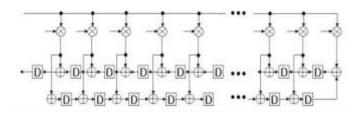

Fig.1. N-tap transposed FIR filter

Fig 2. Dynamic partial reconfiguration

## Several styles DPR

Xilinx inc. Suggests in two simple types of dynamic reconfiguration on a single FPGA: the Difference-based totally partial reconfiguration and the module-based totally partial reconfiguration. Difference based totally partial reconfiguration can be used when a small exchange is made to the layout. It is specially beneficial in case of converting Look-Up Table (LUT) equations or dedicated reminiscence blocks content. The partial bitmovement consists of simplest data about variations among the cutting-edge design structure (that is living in the FPGA) and the new content material of an FPGA. Switching the configuration of a module from one implementation to another is very quick, because the bitstream variations can be extraordinarily smaller than the entire device bit-circulation. Module-primarily based partial reconfiguration makes use of modular layout ideas to reconfigure huge blocks of common sense. The awesome portions of the layout to be reconfigured are known as reconfigurable modules. Because specific residences and particular format standards must be met with admire to a reconfigurable module, any FPGA design proceeding to use partial reconfiguration should be deliberate and laid out with that during thoughts.

Finite Impulse Response (FIR) filters are the maximum basic elements in digital sign processing that are

commonly enforced on dedicated hardware in place of software for pace computation. Due to the need of low power excessive velocity implementation of FIR filter in various embedded programs, it's vital to implement the reconfigurable filter architectures supported electricity or sources problems, or simply to implement new practicality on the run. FPGA is one such platform that lets in adapting hardware assets to fulfill time-varying requirements in electricity, sources, or performance and at identical time retaining an sincere speed of operation. Many of the low in cost hardware architectures are evolved to the exploitation of the reconfigurable and non reconfigurable architectures. One in every of the mission in partial reconfigurable architectures is that the reconfigurable overhead, this is that the time spent for reconfiguration at the fly because of the device best and reconfiguration time of the FIR filter will boom with the rise in filter order and type of mathematics used. As multipliers devour extra electricity in multiply and Accumulate (MAC) operation many multipliers much less schemes are projected. Fig.1: Structure of FIR Filter MCM is worried to deliver constant multiplication in DSP systems, MIMO (Multiple Input Multiple Output) systems, and Frequency multiplication, Error correcting codes, Graphics and management packages. In such applications full fledge of multipliers aren't required. Since coefficient are regular to supply regular multiplication. Once the MCM layout is made, it can be known as time and again it wished. Constant multiplication either can be performed by means of digit parallel fashion or digit serial technique. Digit parallel method of constant multiplier desires external cord for transferring. It needs a number of space while implementation takes area in FPGA or the other ASIC. Thus digit serial approach overcomes area constrain with ideal delay temporal order. Multiplication with steady is termed steady multiplication.

This approach is hired in filter operation. There are 2 varieties of consistent multiplication. One is Single Constant Multiplication and any other one is Multiple Constant Multiplication. Input is expanded with single unique steady to supply output is termed SCM. Canonical Signed Digit (CSD) variety example is employed to enforce SCM multipliers. Input is accelerated with a couple of numbers of unique coefficients to supply multiple outputs is called MCM. Multiplication can be a way of transferring and addition operation. Constant multiplier issue consists of sort of adder, substractor and shifter in line with the regular combine.

## 4. Research Methodology/Planning of Work

On adaptive systems, a restrained aspect for the overall machine Performance is frequently the rate of which the device is able to adapt to carry out a sure mission. This phase describes the Implementation method of 20-tap FIR filter, which can Reconfigured in part from 8-faucet to most 20-tap FIR filter. The entire gadget is applied on a Xilinx Virtex-four FPGA A. HDL layout description and Synthesis Partial reconfiguration calls for a hierarchical layout technique that ought to be strictly followed at some point of the HDL coding manner. The first step of the PR layout flow is to outline 3kinds of HDL layout description after which synthesize those HDL descriptions one after the other.

These HDL layout descriptions are composed to following three layout modules.

\* Top-stage design module: In this step, we should remember every sub-module interconnection using bus macro and location undertaking. Top-level description ought to only comprise I/0, Clock primitive, Base design, PR module, bus-macro instantiations and signal declarations.

\* Base layout module: Base design module is static design module this means that that base design module will now not reconfigure although partial reconfiguration is done. Therefore, this step is same to conventional HDL layout technique. But dressmaker need to bear in mind enter and output assign rule for partial reconfiguration.

\* PR design module: PR module is likewise identical to traditional HDL design approach. However PR module can exist two or greater. Therefore dressmaker ought to describe a couple of description of HDL processing. For instance, side detection in snap shots. It is widely used in photo processing to hold edges from snap shots while eliminating the noise.

# 5. Set Design Constrains

After the HDL design description is synthesized, the subsequent step is to location constraint on the design for vicinity and direction (PAR) and timing constraint to enhance the layout performance. Design constraints should have place group, reconfiguration mode and bus macro place constraints.

Implement Base Design First, the base design need to be implemented. The statistics generated via put in force base design is used for partial reconfigurable modules implementation phase.

Implement Partial Reconfigurable Modules After the base design is carried out, every PR modules have to also be carried out. Each of the PR modules should be applied one at a time.

Merge The very last step within the PR design waft is to merge the top, base, and PR modules. During the merge step, a complete layout is built from each PRM and the base design. In this step, many partial bitstreams for each PRM and preliminary full bit streams are created to configure the FPGA.

## 6. CONCLUSION

PR has evolved significantly over latest years, and found use in a numerous range of packages. The layout of PR systems stays tough, and for this reason, only available to FPGA professionals. Many published techniques for overcoming the restrictions of supplier tools have slowly turn out to be obsolete, due to the increasing heterogeneity of present day devices and less open access supplied via vendors. Since many techniques are also heavily tied to unique architectures, with their evolution, these gear can come to be unusable. As a end result of these difficulties, most systems that use PR at present have to be designed at a low level with special hardware layout expertise required. The rising hobby in using FPGAs in the datacenter represents the primary enormous use of PR in deployed systems, and there remain severa demanding situations to completely virtualise FPGA resources the usage of PR. The trends in the direction of more self reliant structures in regions consisting of car, verbal exchange, and aerospace programs additionally presents an opportunity wellapplicable to PR gadget design

#### REFERENCES

[1]. S.-R. Kuang and J.-P. Wang, "Design of power-efficient configurable booth multiplier,"IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 3, pp. 568–580, Mar. 2010.

[2]. W. Ling and Y. Savaria, "Variable-precision multiplier for equalizer with adaptive modulation," in Proc. 47th Midwest Symp. Circuits Syst., vol. 1. Jul. 2004, pp. I 553– 1556.

[3]. Xilinx Inc.: XAPP 290: Two flows for Partial Reconfiguration: Module Based or Difference Based.www.xilinx.com, Sept. (2004).

[4]. O. A. Pfander, R. Hacker, and H.-J. Pfleiderer, "A multiplexer-based concept for reconfigurable multiplier arrays," in Proc. Int. Conf. Field Program. Logic Appl., vol. 3203. Sep. 2004, pp. 938–942.

[5]. H. Lee, "A power-aware scalable pipelined booth multiplier," in Proc. IEEE Int. SOC Conf., Sep. 2004, pp. 123–126.

[6]. Mesquita, D., Moraes, F., Palma, J., Moller, L., Calazanas, N.: Remote and Partial Reconfiguration of FPGAs: tools and trends. International Parallel and Distributed Processing Symposium,(2003).

[7]. Meyer-Baese, U.: Digital Signal Processing with Field Programmable Gate Arrays. Springer, (2001).

[8]. Xilinx Inc.: Development System Reference Guide. www.xilinx.com.

[9]. A. Bermak, D. Martinez, and J.-L. Noullet, "High density 16/8/4-bit configurable multiplier," Proc. Inst. Electr. Eng. Circuits Devices Syst.,vol. 144, no. 5, pp. 272–276, Oct. 1997.

[10]. M. Hatamian and G. L. Cash, "A 70 MHz 8 bit x 8 bit parallel pipelined multiplier in  $2.5 \,\mu$ m CMOS,"IEEE Journal of Solid-State Circuits, vol. 21, no. 4, pp. 505–513, 1986.

[11]. Yeong-Jae Oh, Hanho Lee, Chong-Ho Lee, "A Reconfigurable FIR Filter Design Using Dynamic Partial Reconfguration", IEEE,vol-06, pp. 4851–4854, ISCAS 2006.

[12]. S.Karthick, Dr. s. Valarmathy and E.Prabhu ," RECONFIGURABLE FIR FILTER WITH RADIX-4 ARRAY MULTIPLIER", jatit, Vol. 57 No.3, pp.326-336, Nov.2013.

[13]. K.Anandan and N.S.Yogaananth, "VLSI Implementation of Reconfigurable Low Power Fir Filter Architecture", IJIRCCE, Vol.2, Special Issue 1, pp no 3514-. 3520, March 2014.

[14]. Martin Kumm, Konrad M<sup>°</sup>oller and Peter Zipf "Dynamically Reconfigurable FIR Filter Architectures with Fast Reconfiguration", ieee journal of solid-state circuits, vol. 41, no. 4, april 2006.

[15]. Pramod Kumar Meher, Shrutisagar Chandrasekaran,and Abbes Amira , "FPGA Realization of FIR Filters by Efficient and Flexible Systolization Using Distributed Arithmetic", ieee transactions on signal processing ,pp no-1-9.

[16]. Xiaoxiao Zhang, Farid Boussaid and Amine Bermak, "32 Bit×32 Bit Multiprecision Razor-Based Dynamic Voltage Scaling Multiplier With Operands Scheduler", ieee transactions on very large scale integration (vlsi) systems, vol. 22, no. 4, april 2014.

[17]. K.Gunasekaran and M.Manikandan," High Speed Reconfigurable FIR Filter using Russian Peasant Multiplier with Sklansky Adder", Research Journal of Applied Sciences, Engineering and Technology 8(24): 2451-2456, 2014.

[18]. Shidhartha Das, David Roberts, Seokwoo Lee, Sanjay Pant, David Blaau, Todd Austin, Kriszti**á** Flautner and Trevor Mudge, "Self-Tuning DVS Processor Using Delay-Error Detection and Correction", ieee journal of solid-state circuits, vol. 41, no. 4, april 2006.

[19]. J Britto Pari, et al., "Reconfigurable Architecture Of RNS Based High Speed FIR Filter", Indian Journal Of Engineering And Material Sciences, pp. 230-240, vol.21, april 2014.