International Research Journal of Engineering and Technology (IRJET)Volume: 08 Issue: 05 | May 2021www.irjet.net

# AREA EFFICIENT LOW POWER BUFFER AND BUFFERLESS DATA FLOW

**CONTROL TECHNIQUES FOR CONGESTION AVOIDANCE**

# **IN NoC ARCHITECTURE**

Dr.R. Poovendran<sup>1</sup>, R.N. Aswini<sup>2</sup>, K.T. Lakshmi Priya<sup>3</sup>, T. Lavanya<sup>4</sup>

<sup>1</sup>Associate Professor, <sup>2,3,4</sup>UG Student, Dept. of Electronics and Communication Engineering, Adhiyamaan College of Engineering, Hosur, Tamil Nadu, India.

poovendranr@gmail.com<sup>1</sup>, ashurv007@gmail.com<sup>2</sup>, thilakpriya8@gmail.com<sup>3</sup>, lavsuba6@gmail.com<sup>4</sup>

\*\*\*\_\_\_\_\_\_

**Abstract** - The plan of proficient models for correspondence in on chip multiprocessors framework includes numerous difficulties with respect to the interior switch capacities utilized in Network on Chip (NoC) foundation. This paper proposes an inner switch engineering, for on chip correspondence, carrying out stream control component for blockage aversion with QoS thought. It portrays the inner elements of this switch for ideal yield bounce planning and its ability to apply per-class administration for inbound streams. The paper centers primarily around the portrayal and execution examination of two proposed plans for information stream control that can be utilized with the proposed switch design. The outcomes appeared in this paper demonstrate that the utilization of these proposed plans in NoC accomplishes an intriguing improvement with regards to the deliberate start to finish QoS. We did a broad examination of the proposed arrangements with the current plans distributed in the writing to show that the proposed arrangement beats these, keeping an intriguing compromise with the equipment attributes when planned with 45 nm coordination innovation.

*Key Words*: NoC, QoS delivery, Buffer & Buffer less Congestion, WRED Algorithm

# **1. INTRODUCTION**

The correspondence part of Multi-Processor Systems-on Chip (MP-SoC) is probably the greatest test in the new age of installed frameworks. Inside and out, Networks-on-Chip (NoC) used to interconnect the multi-centers, are described by high transmission capacity joins between the switches because of the of the chip. Be that as it may, the region cost of the memory some portion of the coordinated circuit emphatically restricts the memory limit of the switch, which restricts its capacity to retain substantial traffic blasts. The rest of this paper is coordinated in the accompanying segments. We first overview the fundamental existing commitments in the space of blockage and information stream control in network on chip. We furthermore, present the proposed switch engineering and the proposed plans for information stream and blockage control. We will at that point center around the assessment of the stream control instruments as far as QoS and blockage control. At long last, we examine the equipment qualities of our proposed switch prior to finishing with an end and headings for future work.

# **2. RELATED WORK**

NoC communication, which is portrayed by high bandwidth, has as of late become a functioning exploration territory, fundamentally in regards to the issues of information stream control and blockage the board. The primary objective is to improve the productivity of data transmission distribution while keeping away from switch immersion. Traffic balancing based on a congestion-aware, adaptive routing process is an interesting approach to achieve load fairness (Wang et al., 2012). This arrangement frequently includes a trade of burden states and connection use between neighbors, advancing the directing interaction as per this traded information. The creators in Lotfi-Kamran et al. (2010) read another answer for clog evasion dependent on unique XY directing (DyXY). In their methodology, called Enhanced Dynamic XY (EDXY) steering, every switch signals clog to its neighbors through a useless transport. The introduced arrangement keeps all information streams from attempting to have a similar way, therefore diminishing information gridlock. Execution investigation of this arrangement has shown great outcomes for parcel idleness across these switches, beating the immediate XY steering approach. Nonetheless, this plan didn't address the issue of clog as an overall wonder, which may influence an organization even with traffic dissemination. In Wang et al. (2013), a plan utilizing an energy-and cushion mindful versatile steering calculation (EBAR) was proposed to appropriate nuclear power in a NoC. Clog mindfulness strategies dependent on flagging have been proposed as an effective strategy to share locally the condition of switch cradles (Aci and Akay, 2010; Kaddachi et al., 2008;

Daneshta lab et al., 2012). The expectation is to stay away from clogged zones in the correspondences way. Applying this technique requires broadcasting clog data utilizing extra transports or with extra information conveyed by the flutters. We feel that this technique is intriguing; nonetheless, we accept that iapplication of an adequate flowcontrol mechanism. Ebrahimi et al. (2012) have read another calculation for the steering cycle that utilizes nearby and non-neighborhood network data.

The proposed plot, called the Congestion Aware Trapezoid-Based Routing Algorithm (CATRA), characterizes a bunch of hubs that are probably going to be associated with the information correspondence way dependent on their clog status. The clog data is diffused through an additional transport that permits continuous refreshing without expanding traffic. The paper talked about the equipment execution of this plan, showing that the extra expense to carry out the proposed thought is sensible as far as circuit region and force utilization. While this methodology appears to be appealing for NoC execution, the paper didn't show any improvement to start to finish QoS at the application level, which would be the fundamental contention to legitimize its selection. An approach to flow control was proposed by Becker et al. (2012). The introduced arrangement plans to control the information supports occupation per information stream. The proposed plot decides the credit took into account each virtual channel dependent on execution perceptions. The creators exhibited the effectiveness of this methodology, however they didn't consider its force utilization.

### **3. PROPOSED SYSTEM**

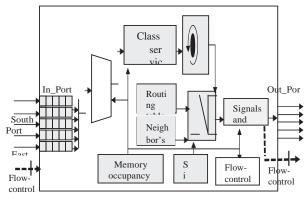

It presents the overall inward architecture of the proposed switch for on-chip communication. It is an upgraded form of the design concentrated in Adel et al. (2014). The principle new commitment concerns the reconciliation of a stream control instrument and the sufficiency of the engineering for productive start to finish QoS.

The proposed design is a particular, versatile framework that incorporates new control and information stream the board capacities. It performs per-bounce preparing as for qualities of the information stream, which is a novel methodology. Bounces format incorporates a bunch of fields making it conceivable to perform granular directing, permitting the switch to deal with passing flutters as indicated by their limitations. In this design, correspondence streams are prepared by their group of administration, with order analyzed as flutters line in the interior memory of the switch. Planning dances into the steering interaction too components identified with blockage evasion depend on this grouping. These interior segments are synchronized by an outside clock signal.

#### 4. METHODOLOGY

Fig-1 Block Diagram

#### 4.1 General protocol structure and flit type

Data flits are transport of data between IPs. During the communication process, three types of data flit are required.

**1.Head-data flit**: The technique is based on route establishment between source and destination IPs..

**2. Continuation-data flit**: This flit is processed after head data flit that transports the data payload. In this flit, the process identifier is used to identify the output port of the connected routers,

**3.End-data flit**: This has the same structure as the data flit, but its arrival triggers the release of resources reserved for the current communication process.

**4.Signaling flits** are generated by a router they carry useful information between neighboring routers

**5.** Approaches to flow control and congestion avoidance, The end-to-end QoS (e.g. end-to-end delay, jitter, and number of lost flits) depends on the capacity of the router to handle.

4.2 Flow control based on the use of an output buffer

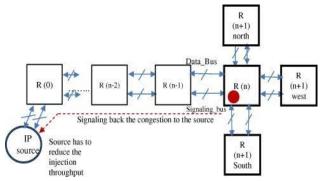

Fig -2 Flow control based on output buffer

In the yield framework control approach, a support at the yield level helps with thwarting the repeat of the upstream data when the accompanying switch is obstructed (Fig. 4). Therefore, we portray three levels that assess the store of a switch: under-stacked, stacked, or obstructed. In this, interminable stock of a hailing skip that shows a stacked memory state in the accompanying switch, a switch authorizes the yield backing to control the yield stream rate. Ricochets are then implanted into the stream control pad from either index\_1 or index\_2, tending to two circumstances in the yield support. Bobs are implanted to index\_1 when the accompanying switch is over-stacked (obstructed), while index\_2 is used when it is in a stacked state. At each specific edge of the clock signal, bobs are time-moved to the yield port. The moves are imbued at index\_3 if the stream control instrument isn't activated. The thinking is to introduce some check cycles before passing on the ripples with the assumption that giving greater chance to the accompanying change to propel moves from its memory to their goal would keep an essential separation from or resolve the blockage.

Let us note by Fi the data-flow of the communication process  $\delta$

Proc InjRat(i) = Num flits(i)

T Clock cycle

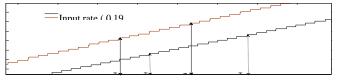

# 4.3 Performance of the WRED-like algorithm

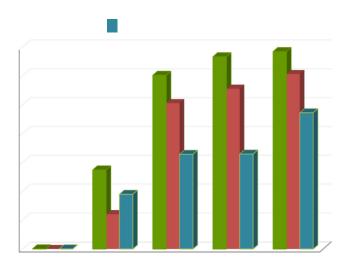

We first assessed the exhibition of the planned WRED-like calculation for disposing of low-significance flits to dump memory and keep away from clog during weighty traffic. To test the capacity of this calculation to oppose clog under substantial burdens, we infused into one switch numerous communication measures on various information ports. Fig. 8 shows the yield of the switch for two distinctive infusion rates (0.23 dances/clk and 0.19 flutters/clk). The moments T1 and T3 are the occasions when blockage is identified in the switch memory for infusion paces of 0.23 dances/clk and 0.19 bounces/clk, separately, without the utilization of the dance disposing of calculation. At the point when the WREDlike calculation is applied, clog events are deferred for both info rates, individually, to T2 and T4. By utilizing the particular dance disposing of interaction, the switch deferred the blockage by more than 180 and 200 clk cycles for input paces of 0.23 and 0.19 flutters/clk, individually. The capacity of the WRED-like calculation to postpone blockage is higher with a lower infusion rate.

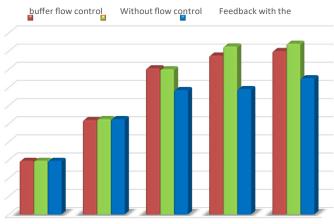

Under low organization load (0.12 flutters/clk cycle), the organization conveys the bounces to the beneficiary with practically a similar greatest jitter. Notwithstanding, under higher organization load, which causes clog (from 0.56 dances/clk cycles), the plan dependent on an input flagging instrument to the source center guarantees less jitter contrasted with the yield cradle stream control system or contrasted with correspondence with no stream control component. At a heap of 0.56 bounces/clk cycle, the most extreme estimated estimation of jitter is higher while applying the input flagging control component than while applying both of the two different plans. Truth be told, at this heap the memory of the switch is gently stacked, the yield support stream control component begins time-moving the dances at the yield (list 2) without lessening the infusion pace of the source. This high information infusion rate favors infusing more flutters of a similar information stream in the clogged switch and thusly conveying more bounces to the gathering. In any case, the input stream control instrument lessens the infusion pace of the source considerably and afterward it begins expanding it gradually to keep away from blockage.

# 4.4 Hardware characteristics of the proposed router

To assess the equipment highlights of the read switch for on chip correspondence, a NoC switch has been intended for ASIC CMOS prototyping. We utilized a VHDL depiction at the RTL level to portray the functionalities of the switch as sets of Expanded Limited States Machines.

Indeed, for a recurrence of 500 MHz, they involve about 0.0002 mm2 of the circuit territory and around 0.1 mW of the unique force utilization. These costs increment somewhat with recurrence increment, needing about 0.004 mm2 more between 330 MHz and 1 GHz utilizing this combination innovation.

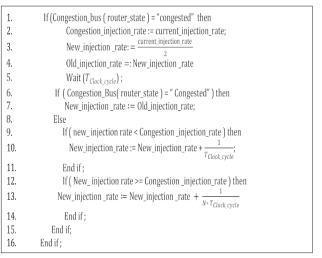

Fig - 4 Pseudo-code of the injection-rate control algorithm

International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056 Volume: 08 Issue: 05 | May 2021 www.irjet.net IRIET

p-ISSN: 2395-0072

## **5. RESULTS AND DISCUSSION**

Chart -1 End to end delay measured for different flow control schemes.

Chart - 2 Dropped flits during congestion with different flow-control s c h e m e s

Figure shows that the results of buffer and buffer less congestion Fig 5.1 shows that buffer are detected and Fig 5.2 shows the buffer less are detected by using wred processing technique.

### **6. CONCLUSIONS**

The first flow-control scheme involves an output buffer to delay flit forwarding to a congested router based on a signaling process between neighbors. The second studied scheme applies a feedback-signaling mechanism to the source core to reduce the injection rate. These two proposed flow control schemes were applied alongside a WRED-like algorithm that selects low-importance flits to be dropped out of memory during congestion avoidance and resolution. This algorithm to unload the memory of congested routers is intended to reduce distortion on the QoS at the reception level. We measured the performance of the two proposed

flow-control schemes when applied to a multiprocessor architecture, which demonstrated the efficiency of the two proposed schemes. In particular, the feedback-signaling scheme has shown attractive performance compared to the output buffer flow-control process.

## **7. FUTURE ENHANCEMENT**

For Future Work, we believe that the plan of a powerful stream control instrument which thinks about the requirements of the particular information stream that overburdens the organization could be a fascinating way to deal with expand the versatility of the proposed switch. Also, we accept that planning the switch with a nonconcurrent inside engineering would improve the force utilization of the proposed design, which may make it more appealing for use in low-power applications.

### REFERENCES

- [1] Aci, C.I., Akay, M.F., 2010. A new congestion control algorithm for improving the performance of a broadcast-based multiprocessor architecture. J. Parallel Distrib. Comput. 70, 930-940.

- [2] Adel, Soudani, Aldammas, Ahmed, Al-Dhelaan, Abdullah, 2014. Efficient scheme for congestion control in network on chip with QoS consideration. J. Circuits Syst. Comput. 23, 09.

- [3] Ascia, G., Catania, V., Palesi, M., Patti, D., 2006. A new selection policy for adaptive routing in network on chip. In: Proceedings of the 5th WSEAS International Conference on Electronics, Hardware, Wireless and Optical Communications, pp. 94–99.

- [4] Barbera, M., Lombardo, A., Schembra, G., Trecarichi, A., 2008. Improving fairness in a WRED-based DiffServ network: a fluidflow approach. Perform. Eval. 65, 759-783.

- Becker, D.U., Jiang, N., Michelogiannakis, G., Dally, W.J., 2012. [5] Adaptive backpressure: efficient buffer management for on-chip networks. In: IEEE 30th International Conference on Computer Design (ICCD), pp. 419-426.

- Bolotin, E., Cidon, I., Ginosar, R., Kolodny, A., 2004. QNoC: QoS [6] architecture and design process for network on chip. J. Syst. Architect. 50, 105–128. Chen, Y.-J., Yang, C.-L., Chang, Y.-S., 2009.

### **BIOGRAPHY:**

Dr. R. Poovendran, Associate Professor, **Electronics And Communication Engineering Department**, Adhiyamaan College of Engineering, Anna University.