# IMPACT OF DIELECTRIC MATERIALS IN DUAL SOURCE TFET'S GATE VOLTAGE VS DRAIN>GATE AND DRAIN>SOURCE CHARACTERISTICS

M.PRIYANKA<sup>1</sup>, S.BAULKANII<sup>2</sup>

<sup>1</sup>M.PRIYANKA :Student, Dept of ECE,GCE-Tirunelveli, TamilNadu, India <sup>2</sup>S.BAULKANI :Professor, Dept of ECE,GCE-Tirunelveli, TamilNadu, India

\*\*\*\_\_\_\_\_

**Abstract** - Dielectric material is used to increase the high conductance which provides low leakage current. Using various dielectric materials in dual source TFET to analyze the impact in gate voltage Vs drain>gate and drain>source. Highk dielectric materials give better performance than low k dielectric materials. The impact of dielectric materials in dual source TFETs gate voltage Vs drain>gate and drain>source characteristics is done using Silvaco-Atlas TCAD to understand the better behavior.

#### Key Words: TFET (Dual source), quantum tunnelling(band to band), High conductance, drain>gate, drain>source

# **1. INTRODUCTION**

The Tunnel Field Effect Transistors (TFET) is an experimental type transistor. Its structure is very similar to the MOSFET but the switching mechanism makes TFET more effective in low power electronics. TFETs switch by modulating band to band tunnelling mechanism instead of thermionic emission in MOSFET. Transistor speed is proportional to the ON current. Increasing the ON current makes the transistor faster to charge its capacitive load. Dual source TFET structure contains two sources therefore high number of electrons are liberated and provides more current, therefore dual source TFET are more effective than the dual gate TFET. Also dual gate TFET occupies more space than the dual source TFET. Gate voltage plays a major role in the FET. Here the gate voltage Vs Drain>gate and drain> source is the major consideration. Using various dielectric materials in the Dual source TFET structure for analyzing the impact in gate voltage Vs drain>gate and drain>source.

# **1.1 PRINCIPLE**

The TFET switching mechanisms is band-to-band tunnelling (BTBT). When the high voltage is applied to gate then the band bend at the source, Band to Band tunnelling occurs when the conduction band of the intrinsic region aligns with valence band of the P- region. Electrons from the valence band tunnel into the conduction band then current flow will happen. When the gate bias decreased, then misalign happens between the conduction band of the intrinsic region and valence band of the P-region, then there is no current flow. The TFET can switch on and off at the lower voltage than the MOSFET. TFET works on the band to band

tunnelling mechanism of charge carrier from source to channel provides low power consumption.

## **1.2 DIELECTRIC MATERIALS**

Dielectric materials with high dielectric constants can be used as gate dielectric material in TFET. The dielectric material used in this paper is hafnium dioxide, silicon dioxide and silicon nitride. High-k dielectric material gives high value of gate voltage Vs drain>gate and drain>source characteristics. The dielectric layers with high electrical permittivity are used for thickness to provide low leakage current and increases the reliability of the gate dielectric layer. High-k dielectric materials are having the properties of high dielectric constant, low leakage current, power consumption is very small, small tunneling effect, steady in silicon substrates. High k dielectric materials provide better gate voltage Vs drain>gate and drain>source characteristic curve than the Low k dielectric materials.

# 2. PROPOSED MODELLING

The proposed system designs an optimal dual source tunnel FET structure using dielectric materials of  $HfO_2$ ,  $SiO_2$ , and  $Si_3N_4$  to analyze the impact of gate voltage Vs drain>gate and drain>source characteristics. TFETs are mainly used for their effective characteristics in the low power electronics and it very simple in its structure too.

This work explores the potential of high-k dielectric materials is improving the performance of gate voltage Vs drain>gate and drain>source in Dual source TFET. High k dielectric material has the ability to conduct large amount of electrical current. Dielectric materials of HfO<sub>2</sub>, SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> in dual source TFET are analyzed to get the better performance of gate voltage Vs drain>gate and drain>source.

High-k dielectric materials like hafnium- dioxide (HfO<sub>2</sub>) with high dielectric constant give better gate voltage Vs drain>gate and drain>source characteristics than the low k dielectric materials. The impact of various dielectric materials in dual source TFETs gate voltage Vs drain>gate and drain>source is done using Silvaco-Atlas TCAD.

© 2022, IRJET |

www.irjet.net

# **3. RESULT AND DISCUSSION**

#### STRUCTURE FILE:

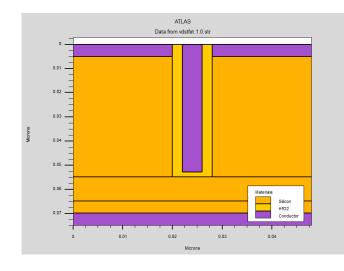

The structure file provides the structure of the simulated device. This file shows various materials used in source region, channel region and gate dielectric of dual source TFET structure. The net doping concentration, electric field of the simulated device can be analyzed using this file.

The following figure shows the structure file of dual source:

#### Fig- 1 Structure of Dual source TFET using dielectric material Hafnium dioxide (HfO<sub>2</sub>)

Fig-1 shows the dual source TFET using Hafnium dioxide material. Silicon dioxide and silicon nitride dielectric materials is used in this structure will give various color in dielectric region.

#### LOG FILE:

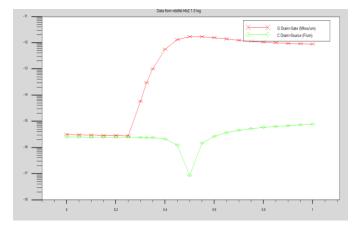

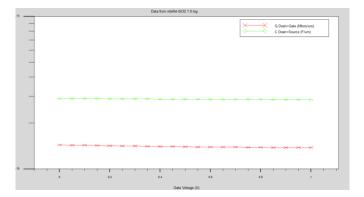

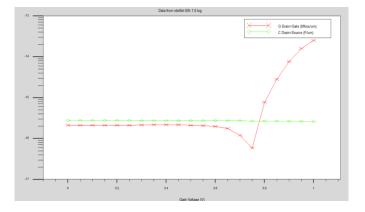

The log file represents the Gate voltage Vs drain>gate and drain>source parameters:

> If the gate to source voltage  $V_{GS}$  increases, then the drain current I<sub>D</sub> also increases. If the gate to source voltage  $V_{GS}$  decreases, then the drain current I<sub>D</sub> also decreases. If the depletion width increases  $V_{GS}$  decreases and if the depletion width decreases V<sub>GS</sub> increases.

Fig-2 Gate voltage Vs Drain>gate and Drain>source curve of dual source TFET using the dielectric material hafnium dioxide (HfO<sub>2</sub>)

Fig- 3 Gate voltage Vs Drain>gate and Drain>source curve of dual source TFET using the dielectric material silicon dioxide (SiO<sub>2</sub>)

Fig-4 Gate voltage Vs Drain>gate and Drain>source curve of dual source TFET using the dielectric material silicon Nitride (Si<sub>3</sub>N<sub>4</sub>)

### **4.CONCLUSION**

The Fig 2, 3 and 4 shows that the high k dielectric material hafnium dioxide provides high gate voltage Vs drain>gate and drain>source characteristics curve compared to the low k dielectric material silicon dioxide and silicon nitride. The high dielectric constant value of 16.64 of hafnium dioxide which reduces leakage current. The implementation of highk dielectrics in FETs is mainly to allow further miniaturization. The leakage current of FETs with HfO<sub>2</sub> as gate dielectric is lower than the SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> and give high value of gate voltage Vs drain>gate and drain>source. The gate voltage Vs drain>gate and drain>source are the major considerations in the low leakage current structures explored in this work. The Low k dielectric materials which cause more leakages. High K dielectrics material allows the gate capacitance to be increased without the leakage effects. It is concluded that due to the high dielectric constant high k dielectric material hafnium dioxide produced the high gate voltage Vs drain>gate and drain>source characteristics than the low k dielectric material silicon dioxide and silicon nitride.

#### REFERENCES

[1] Soniya badgujjar,Girish Wadhwa,Shailendra singh(2019),Design and Analysis of Dual source vertical Tunnel Field Effect Transistor for High Performance,2019 Transaction on Electrical and Electronic Materials.

[2]Ramanathan Gandhi,Zhixianchen (2018) Vertical Si nanowire n-type TFET with low subthreshold swing (50mV/decade) at room temperature,2018 IEEE transaction on electron device, Vol.32, No.4.

[3] Saurabh Sant, Andreas Schenk (2017), Trap tolerant device geometry for InAs/Si TFET,2017 IEEE, Vol.38, No.10.

[4] Saurabh sant, KirstenMoselund, David (2016), Lateral InAs/Si p type TFET integrated on Si simulation study of the impact of interface traps,2016 IEEE transaction, Vol.63, No.11.

[5] V.K. Chinni, Christophe (2016), V-shaped InAs/Al0.5Ga0.5 vertical TFET on GaAs subtract with on current 433uA/um at  $V_{DS}$ =0.5, 2016, Journal of the electron device society, Vol.5, No.1.